# **Preliminary User's Manual**

# $\mu$ PD784218, 784218Y SUBSERIES

# 8-/16-BIT SINGLE-CHIP MICROCONTROLLERS

# **HARDWARE**

| μ <b>PD</b> 784217 | $\mu$ PD784217Y  |

|--------------------|------------------|

| $\mu$ PD784218     | $\mu$ PD784218Y  |

| <b>μPD78F4218</b>  | $\mu$ PD78F4218Y |

[MEMO]

#### **NOTES FOR CMOS DEVICES -**

#### 1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

**EEPROM** and **IEBus** are trademarks of **NEC** Corporation.

Windows and WindowsNT are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation in the USA.

SPARCstation is a trademark of SPARC International, Inc. in the USA.

SunOS is a trademark of Sun Microsystems, Inc. in the USA.

HP9000 Series 700 and HP-UX are trademarks of Hewlett-Packard Company in the USA.

NEWS and NEWS-OS are trademarks of Sony Corporation.

Ethernet is a trademark of Xerox Corporation in the USA.

OSF/Motif is a trademark of Open Software Foundation, Inc.

TRON is an abbreviation of The Realtime Operating system Nucleus.

ITRON is an abbreviation of Industrial TRON.

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

License not needed :  $\mu$ PD78F4218, 78F4218Y

The customer must judge the need for license :  $\mu$ PD784217, 784218Y, 784218Y

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

Purchase of NEC I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M5 96.5

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- · Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.1.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### **NEC Electronics (Germany) GmbH**

Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

### **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### **NEC Electronics (France) S.A.**

Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Singapore Pte. Ltd.**

United Square, Singapore 1130 Tel: 253-8311

Fax: 250-3583

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

#### **NEC do Brasil S.A.**

Cumbica-Guarulhos-SP, Brasil

Tel: 011-6465-6810 Fax: 011-6465-6829

J97. 8

[MEMO]

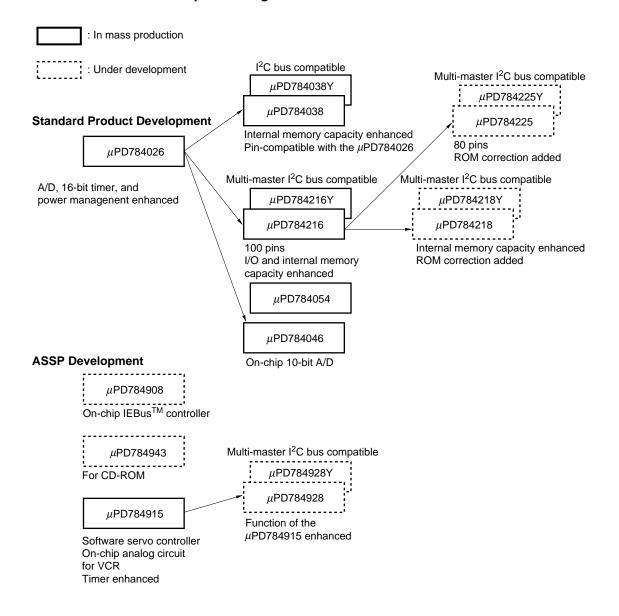

#### INTRODUCTION

**Readers** This manual is intended for user engineers who wish to understand the functions of the

$\mu$ PD784218 and 784218Y Subseries and design its application systems.

Purpose This manual is intended to help users understand the hardware functions of the

$\mu$ PD784218 and 784218Y Subseries.

Organization The  $\mu$ PD784218 and 784218Y Subseries User's Manuals consist of two volumes,

Hardware (this manual) and Instruction.

Hardware Instruction

Pin functions CPU functions

Internal block functions Addressing

Interrupts Instruction set

Other on-chip peripheral functions

There are cautions associated with using this product.

Be sure to read the cautions in the text of each chapter and the summary at the end of each chapter.

How to read this manual

Reading this manual requires general knowledge about electronics, logic circuits, and microcontrollers.

#### • If there are no particular differences in functions

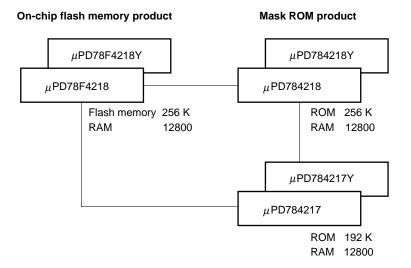

The  $\mu$ PD784218 of the  $\mu$ PD784218 Subseries is described as the representative mask ROM product, and the  $\mu$ PD78F4218 is described as the representative flash memory product.

#### • If there are differences in functions

Each product name is presented and described individually.

Since  $\mu$ PD784218 Subseries products are described as the representative products even in this case, for information on the operation of  $\mu$ PD784218Y Subseries products, read the sections on the  $\mu$ PD784217Y, 784218Y, and 78F4218Y instead of the  $\mu$ PD784217, 784218, and 78F4218.

- · To understand the overall functions

- → Read this manual in the order of the **CONTENTS**.

- · For unusual operations when debugging

- $\rightarrow$  See the applicable cautions listed at the end of each chapter.

- · To check the details of a register whose name is known

- → See APPENDIX D REGISTER INDEX.

- · To learn details of the instruction functions

- → Refer to the 78K/IV Series User's Manual Instruction (U10905E).

- · For application examples of the functions

- → Refer to the application notes (published separately).

#### Differences between the $\mu$ PD784218 Subseries and the $\mu$ PD784218Y Subseries

The only functional difference between the  $\mu$ PD784218 Subseries and  $\mu$ PD784218Y Subseries is the clock-synchronized serial interface. The two subseries otherwise share the same functions.

#### Caution -

The clock-synchronized serial interface is described in the following two chapters.

- CHAPTER 18 3-WIRE SERIAL I/O MODE

- CHAPTER 19 I<sup>2</sup>C BUS MODE (μPD784218Y SUBSERIES ONLY)

For an overview of the serial interface, read CHAPTER 16 altogether.

Legend Data significance : The left side is the most significant digit. The right side is the

least significant digit.

Active low notation :  $\overline{\times}\overline{\times}$  (overbar on pin or signal name)

Note : Description of Note in the text

: Decimal numbers ..... ××××

: Hexadecimal numbers ... ××××H

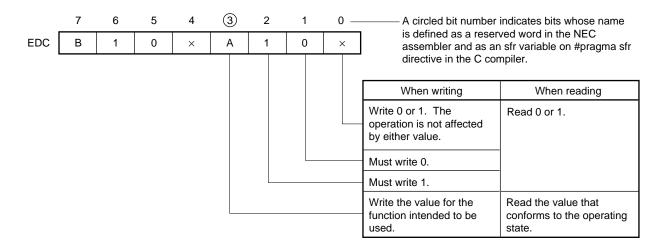

#### Register notation

Never write a combination of codes that have "Setting prohibited" written in the register description in this manual.

Characters that are easily confused: 0 (zero), O (capital o)

: 1 (one), I (letter I), I (capital i)

#### **Related documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

#### Documents related to devices

| Decument Name                                             | Document Number |          |  |

|-----------------------------------------------------------|-----------------|----------|--|

| Document Name                                             | English         | Japanese |  |

| μPD784217, 784218 Preliminary Product Information         | U12303E         | U12303J  |  |

| μPD78F4218 Preliminary Product Information                | U12439E         | U12439J  |  |

| $\mu$ PD784218 Subseries Special Function Register Table  | _               | U12918J  |  |

| μPD784217Y, 784218Y Preliminary Product Information       | U12304E         | U12304J  |  |

| μPD78F4218Y Preliminary Product Information               | U12440E         | U12440J  |  |

| $\mu$ PD784218Y Subseries Special Function Register Table | _               | U12919J  |  |

| μPD784218, 784218Y Subseries User's Manual — Hardware     | This manual     | U12970J  |  |

| 78K/IV Series Application Note — Software Basics          | _               | U10095J  |  |

| 78K/IV Series User's Manual — Instruction                 | U10905E         | U10905J  |  |

| 78K/IV Series Instruction Table                           | _               | U10594J  |  |

| 78K/IV Series Instruction Set                             | _               | U10595J  |  |

#### Documents related to development tools (User's Manuals)

| Document Name                                                                                          |                                                        | Document Number |                |  |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------|----------------|--|

|                                                                                                        |                                                        | English         | Japanese       |  |

| RA78K4 Assembler Package                                                                               | RA78K4 Assembler Package Operation                     |                 | U11334J        |  |

|                                                                                                        | Language                                               | U11162E         | U11162J        |  |

| RA78K4 Structured Assembler Prep                                                                       | rocessor                                               | U11743E         | U11743J        |  |

| CC78K4                                                                                                 | Operation                                              | U11572E         | U11572J        |  |

|                                                                                                        | Language                                               | U11571E         | EEU-961        |  |

| CC78K Series Library Source File                                                                       |                                                        | _               | U12322J        |  |

| IE-78K4-NS                                                                                             |                                                        | To be prepared  | To be prepared |  |

| IE-784000-R                                                                                            |                                                        | EEU-1534        | U12903J        |  |

| IE-784225-NS-EM1                                                                                       |                                                        | To be prepared  | To be prepared |  |

| IE-784218-R-EM1                                                                                        |                                                        | U12155E         | U12155J        |  |

| EP-78064                                                                                               | P-78064                                                |                 | EEU-934        |  |

| SM78K4 System Simulator<br>Windows™ based                                                              | Reference                                              | U10093E         | U10093J        |  |

| SM78K Series System Simulator                                                                          | External Part User<br>Open Interface<br>Specifications | U10092E         | U10092J        |  |

| ID78K4-NS Integrated Debugger                                                                          | Reference                                              | U12796E         | U12796J        |  |

| ID78K4 Integrated Debugger<br>Windows based                                                            | Reference                                              | U10440E         | U10440J        |  |

| ID78K4 Integrated Debugger HP-UX <sup>TM</sup> , SunOS <sup>TM</sup> , and NEWS-OS <sup>TM</sup> based |                                                        | U11960E         | U11960J        |  |

Caution The contents of the above documents are subject to change without notice. Be sure to use the latest edition for designing.

#### Documents related to embedded software (User's Manuals)

| Document Name              |              | Document Number |          |

|----------------------------|--------------|-----------------|----------|

|                            |              | English         | Japanese |

| 78K/IV Series Real-time OS | Basics       | U10603E         | U10603J  |

|                            | Installation | U10604E         | U10604J  |

|                            | Debugger     | _               | U10364J  |

| 78K/IV Series OS MX78K4    | Basics       | _               | U11779J  |

#### Other Documents

| D                                                                                  | Document Number |          |  |

|------------------------------------------------------------------------------------|-----------------|----------|--|

| Document Name                                                                      | English         | Japanese |  |

| IC Package Manual                                                                  | C10943X         |          |  |

| Semiconductor Device Mounting Technology Manual                                    | C10535E         | C10535J  |  |

| Quality Grades on NEC Semiconductor Devices                                        | C11531E         | C11531J  |  |

| NEC Semiconductor Device Reliability/Quality Control System                        | C10983E         | C10983J  |  |

| Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) | C11892E         | C11892J  |  |

| Guide to Quality Assurance for Semiconductor Devices                               | MEI-1202        | _        |  |

| Microcomputer Product Series Guide                                                 | _               | U11416J  |  |

Caution The contents of the above documents are subject to change without notice. Be sure to use the latest edition for designing.

[MEMO]

# **CONTENTS**

| CHAPT | ER 1       | OVERVIEW                                      | 33  |

|-------|------------|-----------------------------------------------|-----|

| 1.1   | Featu      | res                                           | 35  |

| 1.2   | Order      | ing Information                               | 36  |

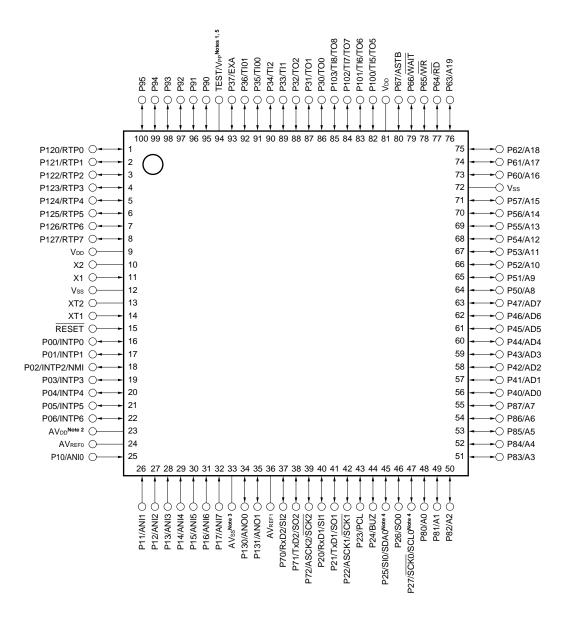

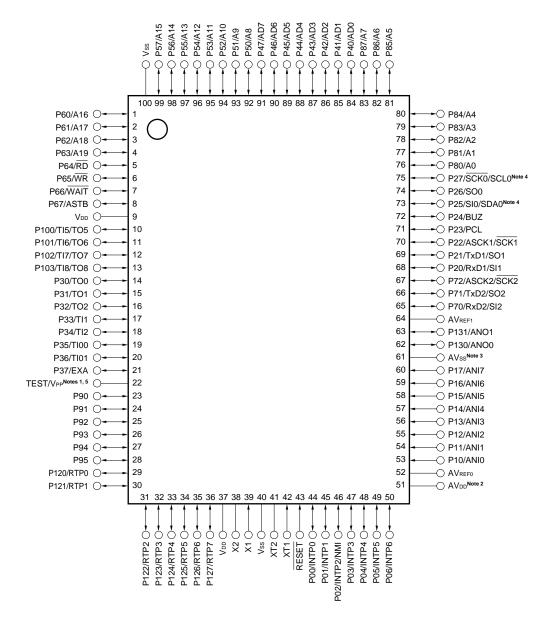

| 1.3   | Pin Co     | onfiguration (Top View)                       | 37  |

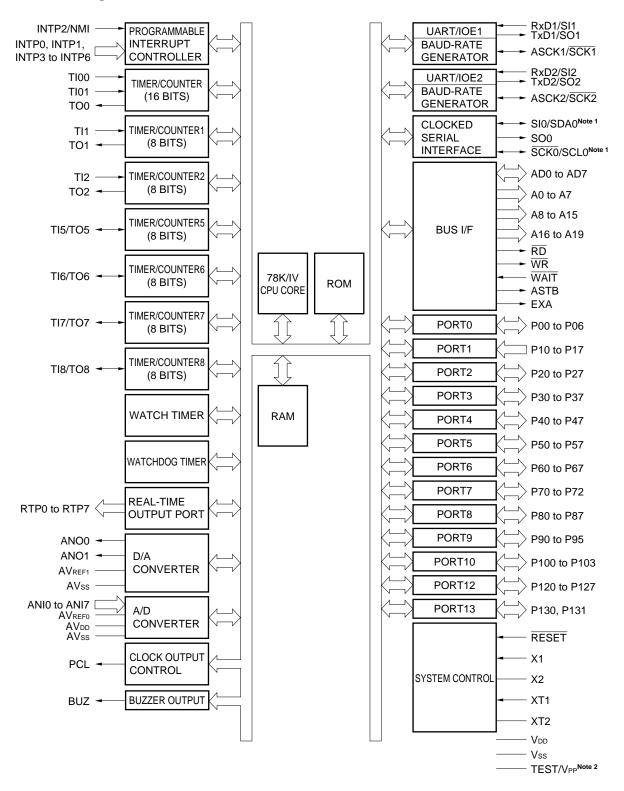

| 1.4   | Block      | Diagram                                       | 40  |

| 1.5   |            | ion List                                      | 41  |

| 1.6   | Differ     | ences among $\mu$ PD784218 Subseries Products |     |

|       | •          | PD784218Y Subseries Products                  |     |

| 1.7   | Differ     | ences between μPD784218 and μPD784216         | 43  |

| CHAPT | ER 2       | PIN FUNCTIONS                                 | 45  |

| 2.1   | Pin Fu     | ınction List                                  | 45  |

| 2.2   |            | ınction Description                           |     |

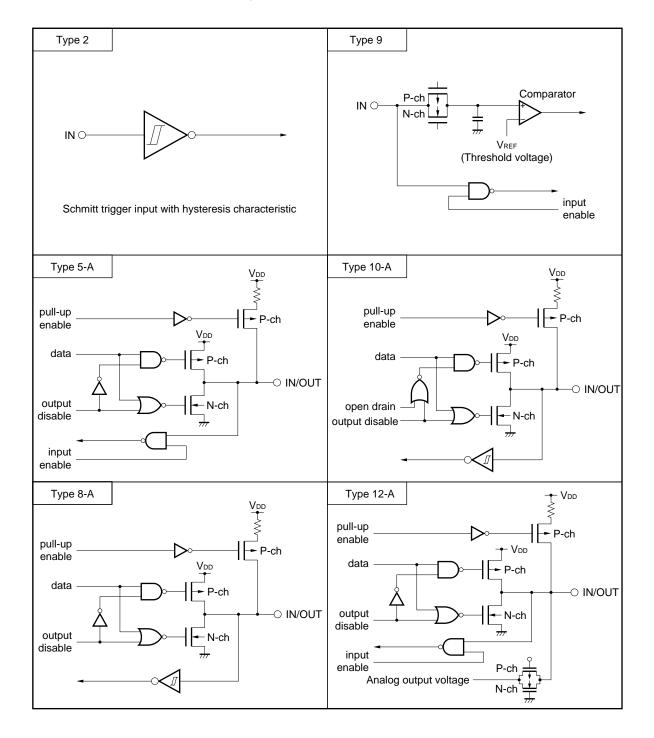

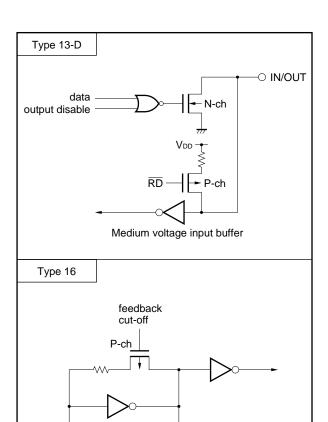

| 2.3   | Pin I/C    | Circuit and Handling of Unused Pins           | 58  |

| CHAPT | ER 3       | CPU ARCHITECTURE                              | 63  |

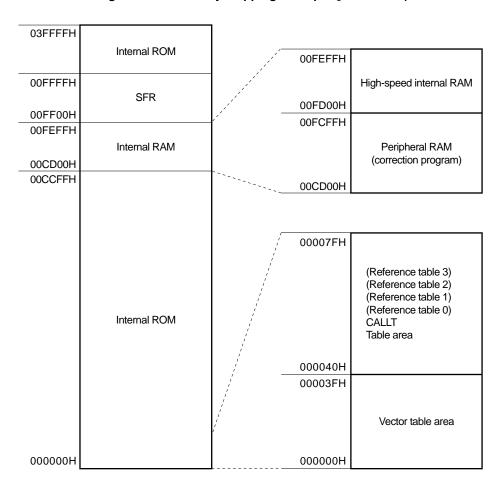

| 3.1   | Memo       | ry Space                                      | 63  |

| 3.2   | Intern     | al ROM Area                                   | 67  |

| 3.3   | Base       | Area                                          | 68  |

|       | 3.3.1      | Vector table area                             | 69  |

|       | 3.3.2      | CALLT instruction table area                  | 70  |

|       | 3.3.3      | CALLF instruction entry area                  | 70  |

| 3.4   | Intern     | al Data Area                                  | 71  |

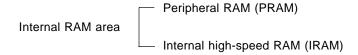

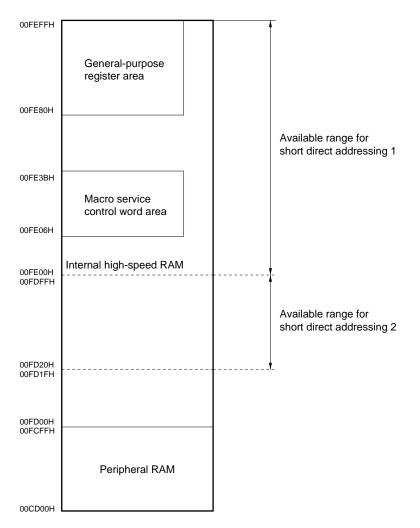

|       | 3.4.1      | Internal RAM area                             | 72  |

|       | 3.4.2      | Special function register (SFR) area          | 75  |

|       | 3.4.3      | External SFR area                             | 75  |

| 3.5   | Exteri     | nal Memory Space                              | 75  |

| 3.6   | $\mu$ PD78 | 3F4218 Memory Mapping                         | 76  |

| 3.7   | Contr      | ol Registers                                  | 77  |

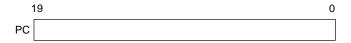

|       | 3.7.1      | Program counter (PC)                          | 77  |

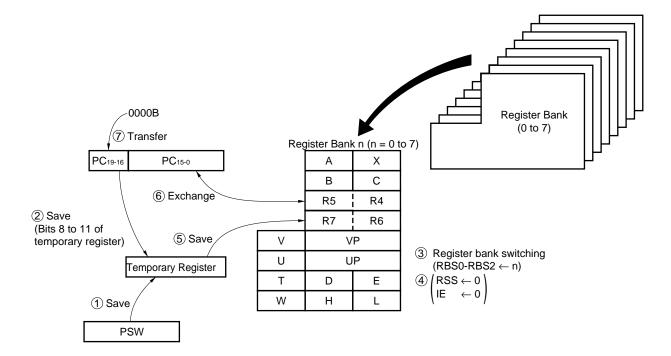

|       | 3.7.2      | Program status word (PSW)                     | 77  |

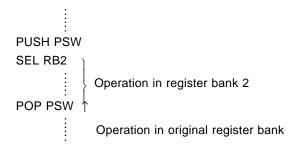

|       | 3.7.3      | Using RSS bit                                 | 81  |

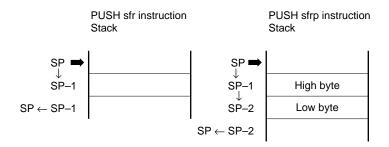

|       | 3.7.4      | Stack pointer (SP)                            | 84  |

| 3.8   | Gener      | al-Purpose Registers                          | 88  |

|       | 3.8.1      | Configuration                                 | 88  |

|       | 3.8.2      | Functions                                     |     |

| 3.9   | •          | al Function Registers (SFRs)                  |     |

| 3.10  | Cautio     | ons                                           | 99  |

| CHAPT | ER 4       | CLOCK GENERATOR                               | 101 |

| 4.1   | Funct      | ions                                          | 101 |

| 4.2   | Config     | guration                                      | 101 |

| 4.3         | Contro  | ol Register                              | 103  |

|-------------|---------|------------------------------------------|------|

| 4.4         | Syster  | m Clock Oscillator                       | 108  |

|             | 4.4.1   | Main system clock oscillator             | 108  |

|             | 4.4.2   | Subsystem clock oscillator               | 109  |

|             | 4.4.3   | Frequency divider                        | 112  |

|             | 4.4.4   | When no subsystem clocks are used        | 112  |

| 4.5         | Clock   | Generator Operations                     | 113  |

|             | 4.5.1   | Main system clock operations             | 114  |

|             | 4.5.2   | Subsystem clock operations               | 115  |

| 4.6         | Chang   | ging System Clock and CPU Clock Settings | 115  |

| CHAPT       | TER 5 I | PORT FUNCTIONS                           | 117  |

| 5.1         | Digital | I Input/Output Ports                     | 117  |

| 5.2         | _       | Configuration                            |      |

| <b>U.</b> _ | 5.2.1   | Port 0                                   |      |

|             | 5.2.2   | Port 1                                   | _    |

|             | 5.2.3   | Port 2                                   |      |

|             | 5.2.4   | Port 3                                   |      |

|             | 5.2.5   | Port 4                                   |      |

|             | 5.2.6   | Port 5                                   |      |

|             | 5.2.7   | Port 6                                   |      |

|             | 5.2.8   | Port 7                                   |      |

|             | 5.2.9   | Port 8                                   |      |

|             | 5.2.10  | Port 9                                   |      |

|             | 5.2.11  | Port 10                                  | 133  |

|             | 5.2.12  | Port 12                                  | 134  |

|             | 5.2.13  | Port 13                                  | 135  |

| 5.3         | Contro  | ol Registers                             |      |

| 5.4         |         | tions                                    |      |

|             | 5.4.1   | Writing to input/output port             | 142  |

|             | 5.4.2   | Reading from input/output port           | 142  |

|             | 5.4.3   | Operations on input/output port          | 143  |

| CUADI       | TED 6 I | REAL-TIME OUTPUT FUNCTIONS               | 1.15 |

| CHAP        | IER O I | VEAL-TIME OUTFUT FUNCTIONS               | 143  |

| 6.1         |         | ions                                     |      |

| 6.2         | Config  | guration                                 | 145  |

| 6.3         | Contro  | ol Registers                             | 148  |

| 6.4         | Opera   | tion                                     | 150  |

| 6.5         | ·       |                                          |      |

| 6.6         | Cautio  | ons                                      | 151  |

| CHAPT       | TER 7   | TIMER/COUNTER OVERVIEW                   | 153  |

| CHAPT       | TER 8 1 | 6-BIT TIMER/COUNTER                      | 157  |

| 8.1         | Functi  | ion                                      | 157  |

| _           |         | guration                                 |      |

| 8.3   | Control Registers                                         | 162 |

|-------|-----------------------------------------------------------|-----|

| 8.4   | Operation                                                 | 168 |

|       | 8.4.1 Operation as interval timer (16-bit operation)      |     |

|       | 8.4.2 Operation as PPG output                             | 170 |

|       | 8.4.3 Operation as pulse width measurement                | 171 |

|       | 8.4.4 Operation as external event counter                 | 178 |

|       | 8.4.5 Operation as square wave output                     |     |

|       | 8.4.6 Operation as one-shot pulse output                  |     |

| 8.5   | Cautions                                                  |     |

| CHAPT | TER 9 8-BIT TIMER/COUNTER 1, 2                            | 191 |

| 9.1   | Functions                                                 | 191 |

| 9.2   | Configuration                                             | 192 |

| 9.3   | Control Registers                                         | 194 |

| 9.4   | Operation                                                 | 199 |

|       | 9.4.1 Operation as interval timer (8-bit operation)       |     |

|       | 9.4.2 Operation as external event counter                 |     |

|       | 9.4.3 Operation as square wave output (8-bit resolution)  |     |

|       | 9.4.4 Operation as 8-bit PWM output                       |     |

|       | 9.4.5 Operation as interval timer (16-bit operation)      |     |

| 9.5   | Cautions                                                  |     |

| 10.1  | Functions                                                 |     |

| 10.1  | Configuration                                             |     |

| 10.2  | •                                                         |     |

| 10.4  | Operation                                                 |     |

| 10.4  | 10.4.1 Operation as interval timer (8-bit operation)      |     |

|       | 10.4.1 Operation as interval timer (o-bit operation)      |     |

|       | 10.4.3 Operation as external event counter                |     |

|       | 10.4.4 Operation as 8-bit PWM output                      |     |

|       | 10.4.5 Operation as interval timer (16-bit operation)     |     |

| 10.5  | ,                                                         |     |

| 10.5  | Cautions                                                  |     |

| CHAPT | TER 11 8-BIT TIMER/COUNTER 7, 8                           | 231 |

| 11.1  | Functions                                                 |     |

| 11.2  | Configuration                                             |     |

| 11.3  | Control Registers                                         | 234 |

| 11.4  | Operation                                                 | 239 |

|       | 11.4.1 Operation as interval timer (8-bit operation)      | 239 |

|       | 11.4.2 Operation as external event counter                | 243 |

|       | 11.4.3 Operation as square wave output (8-bit resolution) | 244 |

|       | 11.4.4 Operation as 8-bit PWM output                      | 245 |

|       | 11.4.5 Operation as interval timer (16-bit operation)     | 248 |

| 11.5  | Cautions                                                  | 249 |

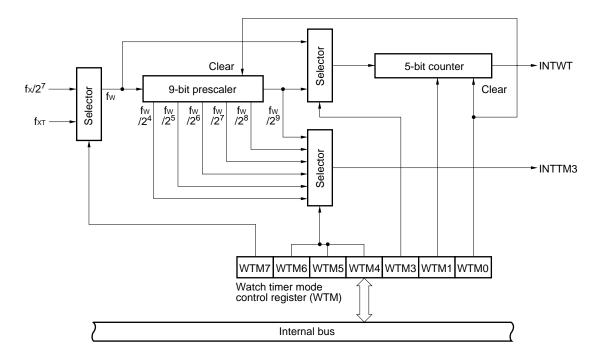

| CHAPT | ER 12 WATCH TIMER                                                                 | 251 |

|-------|-----------------------------------------------------------------------------------|-----|

| 12.1  | Function                                                                          | 251 |

| 12.2  | Configuration                                                                     | _   |

| 12.3  | Control Register                                                                  |     |

| 12.4  | Operation                                                                         |     |

|       | 12.4.1 Operation as watch timer                                                   |     |

|       | 12.4.2 Operation as interval timer                                                |     |

|       |                                                                                   |     |

| CHAPT | ER 13 WATCHDOG TIMER                                                              | 257 |

| 13.1  | Configuration                                                                     | 257 |

| 13.2  | Control Register                                                                  |     |

| 13.3  | Operations                                                                        | 260 |

|       | 13.3.1 Count operation                                                            |     |

|       | 13.3.2 Interrupt priority order                                                   |     |

| 13.4  | Cautions                                                                          |     |

|       | 13.4.1 General cautions when using watchdog timer                                 |     |

|       | 13.4.2 Cautions about $\mu$ PD784218 Subseries watchdog timer                     | 262 |

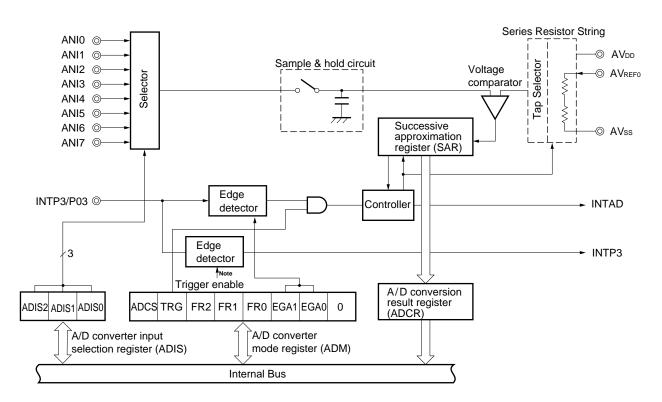

| CHAPT | ER 14 A/D CONVERTER                                                               | 263 |

| 14.1  | Functions                                                                         | 263 |

| 14.2  | Configuration                                                                     | 263 |

| 14.3  | Control Registers                                                                 | 266 |

| 14.4  | Operations                                                                        | 269 |

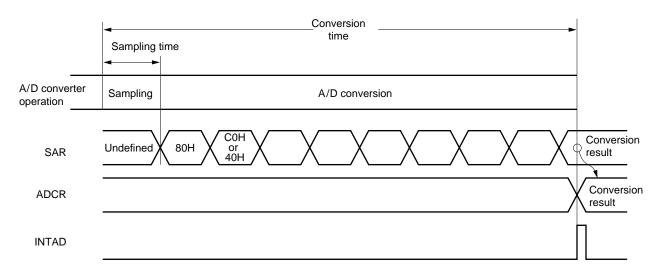

|       | 14.4.1 Basic operations of A/D converter                                          | 269 |

|       | 14.4.2 Input voltage and conversion result                                        | 271 |

|       | 14.4.3 Operation mode of A/D converter                                            | 272 |

| 14.5  | Cautions                                                                          | 274 |

| СНАРТ | ER 15 D/A CONVERTER                                                               | 279 |

| 15.1  | Function                                                                          | 279 |

| 15.2  | Configuration                                                                     |     |

| 15.3  | Control Registers                                                                 |     |

| 15.4  | Operation                                                                         |     |

| 15.5  | Cautions                                                                          |     |

| CHAPT | ER 16 SERIAL INTERFACE OVERVIEW                                                   | 285 |

| CHAPT | ER 17 ASYNCHRONOUS SERIAL INTERFACE/3-WIRE SERIAL I/O                             | 287 |

| 17.1  | Switching between Asynchronous Serial Interface Mode and 3-Wire Serial I/O Mode . | 288 |

| 17.2  | Asynchronous Serial Interface Mode                                                |     |

|       | 17.2.1 Configuration                                                              |     |

|       | 17.2.2 Control registers                                                          |     |

|       | -9                                                                                |     |

| 17.3  | Operation                                                             | 297 |

|-------|-----------------------------------------------------------------------|-----|

|       | 17.3.1 Operation stop mode                                            | 297 |

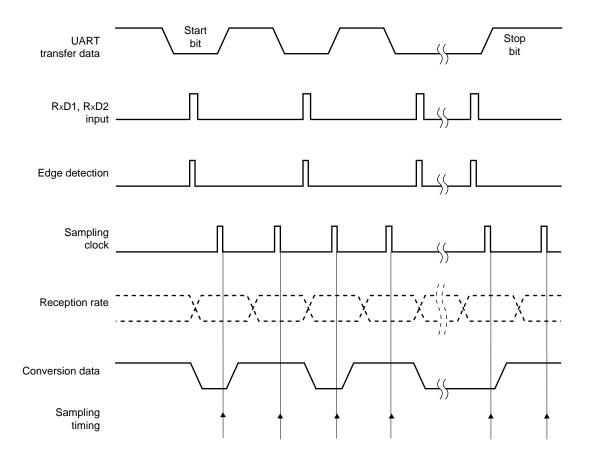

|       | 17.3.2 Asynchronous serial interface (UART) mode                      | 298 |

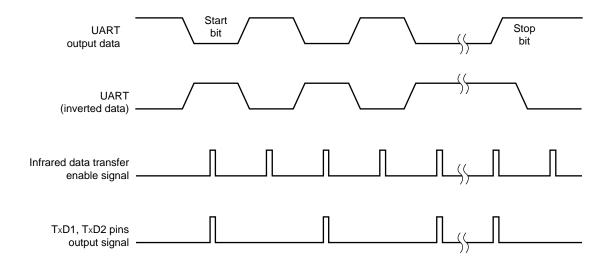

|       | 17.3.3 Infrared data transfer mode                                    | 309 |

|       | 17.3.4 Standby mode operation                                         | 312 |

| 17.4  | 3-Wire Serial I/O Mode                                                | 313 |

|       | 17.4.1 Configuration                                                  | 313 |

|       | 17.4.2 Control registers                                              | 315 |

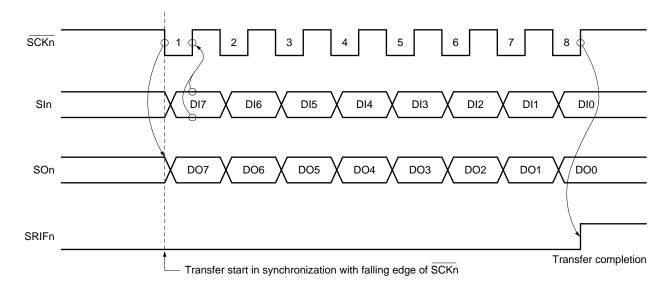

|       | 17.4.3 Operation                                                      | 316 |

| CHAPT | ER 18 3-WIRE SERIAL I/O MODE                                          | 319 |

| 18.1  | Function                                                              |     |

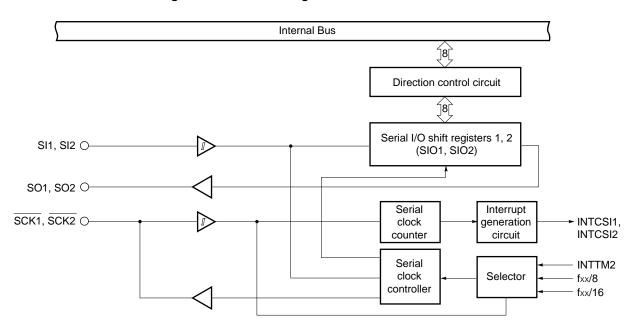

| 18.2  | Configuration                                                         |     |

| 18.3  | Control Registers                                                     |     |

| 18.4  | Operation                                                             | 322 |

| CHAPT | TER 19 I <sup>2</sup> C BUS MODE (μPD784218Y SUBSERIES ONLY)          | 325 |

| 19.1  | Overview of Function                                                  | 325 |

| 19.2  | Configuration                                                         | 326 |

| 19.3  | Control Registers                                                     | 329 |

| 19.4  | I <sup>2</sup> C Bus Mode Function                                    | 341 |

|       | 19.4.1 Pin Configuration                                              |     |

| 19.5  | I <sup>2</sup> C Bus Definitions and Control Method                   |     |

|       | 19.5.1 Start condition                                                |     |

|       | 19.5.2 Address                                                        |     |

|       | 19.5.3 Transfer direction specification                               |     |

|       | 19.5.4 Acknowledge signal (ACK)                                       |     |

|       | 19.5.5 Stop condition                                                 |     |

|       | 19.5.6 Wait signal (WAIT)                                             |     |

|       | 19.5.7 I <sup>2</sup> C interrupt request (INTIIC0)                   |     |

|       | 19.5.8 Interrupt request (INTIIC0) generation timing and wait control |     |

|       | 19.5.9 Address match detection                                        |     |

|       | 19.5.10 Error detection                                               |     |

|       | 19.5.11 Extended codes                                                |     |

|       | 19.5.12 Arbitration                                                   |     |

|       | 19.5.13 Wake-up function                                              |     |

|       | 19.5.14 Communication reservation                                     |     |

|       | 19.5.15 Additional cautions                                           |     |

|       | 19.5.16 Communication operation                                       |     |

| 19.6  | Timing Charts                                                         | 379 |

| CHAPT | ER 20 CLOCK OUTPUT FUNCTION                                           | 387 |

| 20.1  | Functions                                                             | 387 |

| 20.2  | Configuration                                                         | 388 |

| 20.3  | Control Registers                                                     | 388 |

| CHAPT | ER 21   | BUZZER OUTPUT FUNCTIONS                                                                     | 391 |

|-------|---------|---------------------------------------------------------------------------------------------|-----|

| 21.1  | Funct   | ion                                                                                         | 391 |

| 21.2  | Config  | guration                                                                                    | 391 |

| 21.3  | Contro  | ol Registers                                                                                | 392 |

| CHAPT | ER 22   | EDGE DETECTION FUNCTION                                                                     | 395 |

| 22.1  |         | ol Registers                                                                                |     |

| 22.2  | Eage    | Detection of P00 to P06 Pins                                                                | 396 |

| CHAPT | ER 23   | INTERRUPT FUNCTIONS                                                                         | 397 |

| 23.1  | Interru | upt Request Sources                                                                         | 398 |

|       | 23.1.1  | Software interrupts                                                                         | 400 |

|       | 23.1.2  | Operand error interrupts                                                                    | 400 |

|       | 23.1.3  | Non-maskable interrupts                                                                     | 400 |

|       | 23.1.4  | Maskable interrupts                                                                         | 400 |

| 23.2  | Interru | upt Service Modes                                                                           | 401 |

|       | 23.2.1  | Vectored interrupt service                                                                  | 401 |

|       | 23.2.2  | Macro service                                                                               | 401 |

|       | 23.2.3  | Context switching                                                                           | 401 |

| 23.3  | Interru | upt Processing Control Registers                                                            | 402 |

|       | 23.3.1  | Interrupt control registers                                                                 | 404 |

|       | 23.3.2  | Interrupt mask registers (MK0, MK1)                                                         |     |

|       | 23.3.3  | In-service priority register (ISPR)                                                         | 410 |

|       | 23.3.4  | Interrupt mode control register (IMC)                                                       |     |

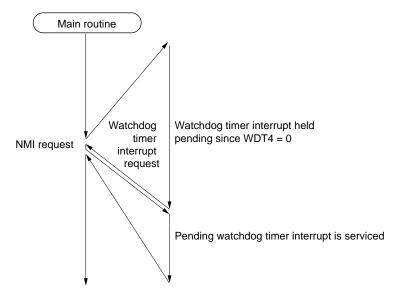

|       | 23.3.5  | Watchdog timer mode register (WDM)                                                          |     |

|       | 23.3.6  | Interrupt selection control register (SNMI)                                                 |     |

|       | 23.3.7  | Program status word (PSW)                                                                   |     |

| 23.4  | Softwa  | are Interrupt Acknowledgment Operations                                                     |     |

|       | 23.4.1  | BRK instruction software interrupt acknowledgment operation                                 |     |

|       |         | BRKCS instruction software interrupt (software context switching) acknowledgment operation. |     |

| 23.5  | -       | nd Error Interrupt Acknowledge                                                              |     |

| 23.6  |         | naskable Interrupt Acknowledge                                                              |     |

| 23.7  | Maska   | able Interrupt Acknowledge                                                                  |     |

|       | 23.7.1  | Vectored interrupt                                                                          |     |

|       | 23.7.2  | Context switching                                                                           |     |

|       | 23.7.3  | Maskable interrupt priority levels                                                          |     |

| 23.8  |         | Service Function                                                                            |     |

|       | 23.8.1  | Outline of macro service function                                                           |     |

|       | 23.8.2  | Types of macro service                                                                      | 431 |

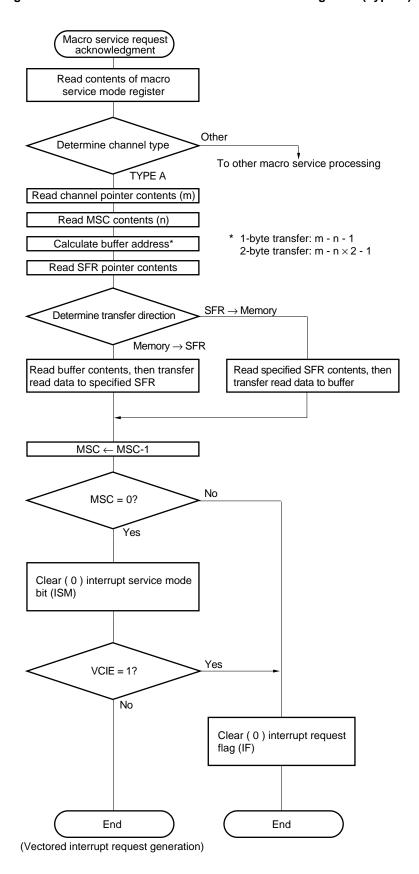

|       | 23.8.3  | Basic macro service operation                                                               |     |

|       | 23.8.4  | Operation at end of macro service                                                           |     |

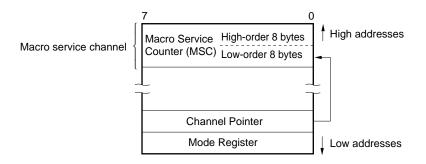

|       | 23.8.5  | Macro service control registers                                                             |     |

|       | 23.8.6  | Macro service type A                                                                        |     |

|       | 23.8.7  | Macro service type B                                                                        |     |

|       | 23.8.8  | Macro service type C                                                                        |     |

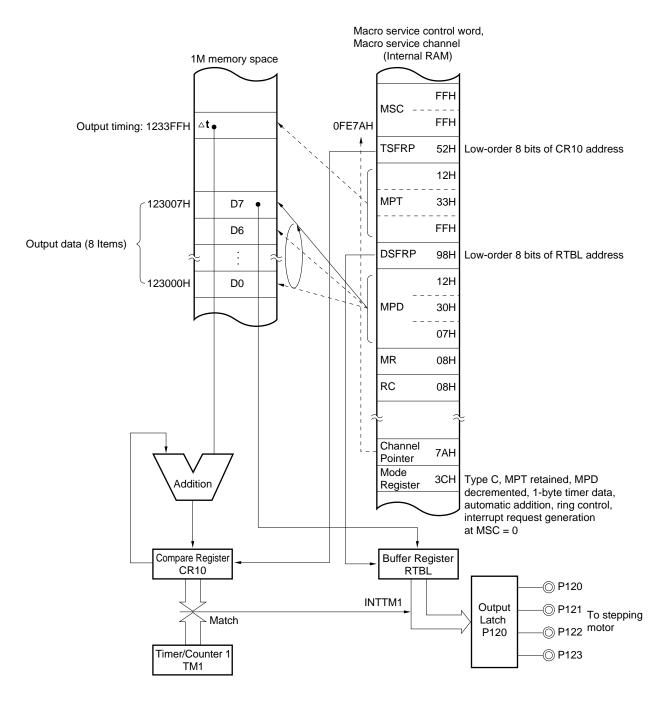

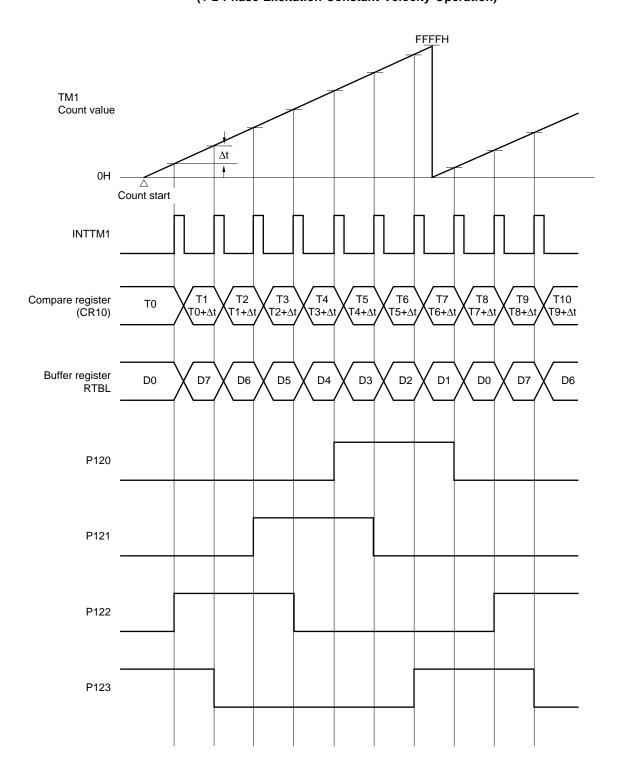

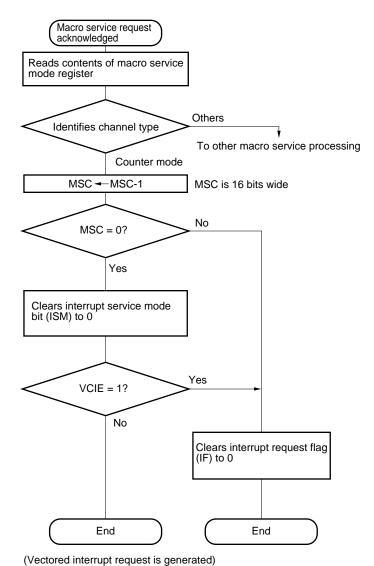

|       | 23.8.9  | Counter mode                                                                                | 466 |

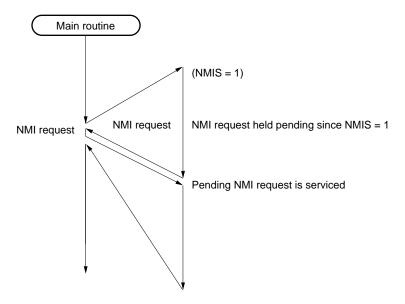

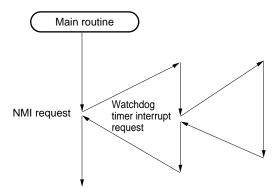

| 23.9     | When I  | nterrupt Requests and Macro Service Are Temporarily Held Pending | 468 |

|----------|---------|------------------------------------------------------------------|-----|

| 23.10    | Instruc | tions Whose Execution is Temporarily Suspended by Interrupt      |     |

|          | or Mac  | ro Service                                                       | 470 |

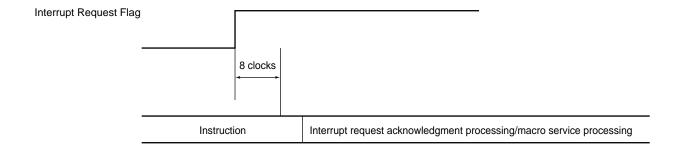

| 23.11    | Interru | pt and Macro Service Operation Timing                            | 470 |

|          | 23.11.1 | Interrupt acknowledge processing time                            | 471 |

|          | 23.11.2 | Processing time of macro service                                 | 472 |

| 23.12    | Restor  | ing Interrupt Function to Initial State                          | 473 |

| 23.13    | Cautio  | ns                                                               | 474 |

|          |         |                                                                  |     |

| CHAPT    | ER 24   | LOCAL BUS INTERFACE FUNCTIONS                                    | 477 |

|          |         |                                                                  |     |

| 24.1     |         | al Memory Expansion Function                                     |     |

| 24.2     |         | l Registers                                                      |     |

| 24.3     |         | y Map for External Memory Expansion                              |     |

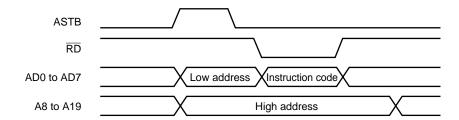

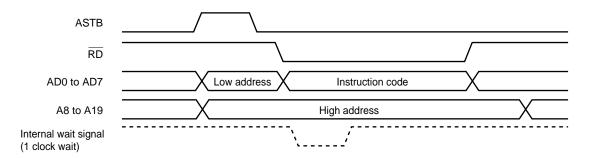

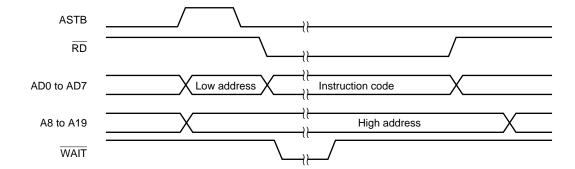

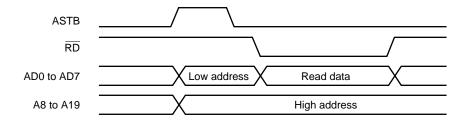

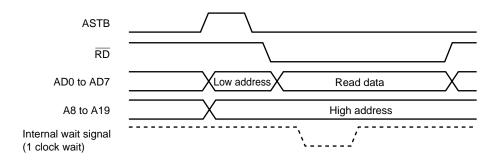

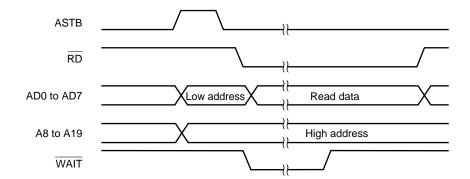

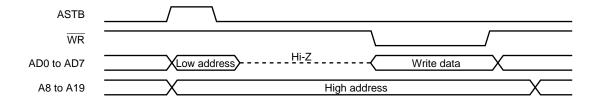

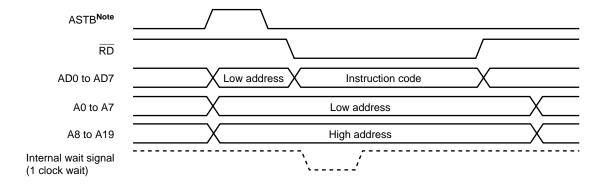

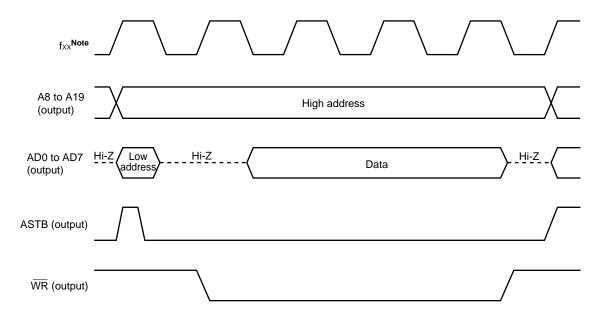

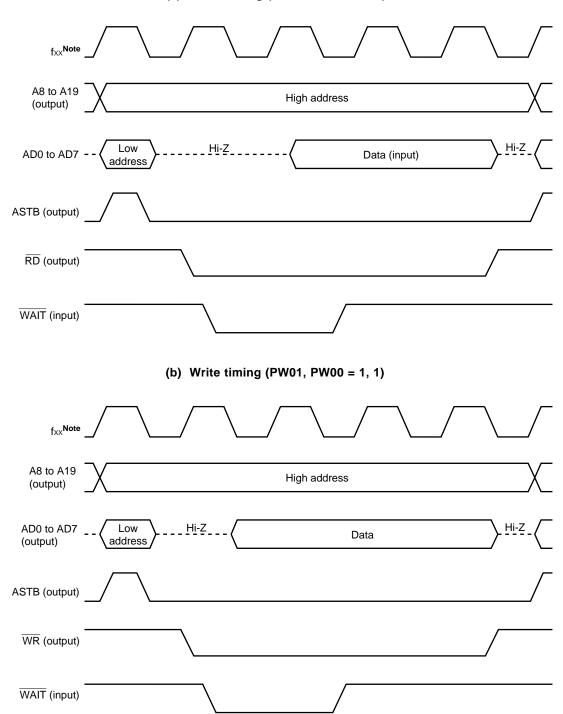

| 24.4     | Timing  | of External Memory Expansion Functions                           |     |

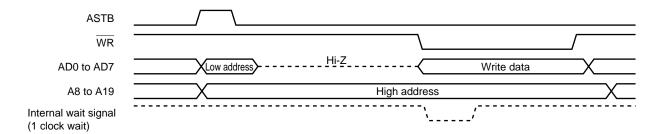

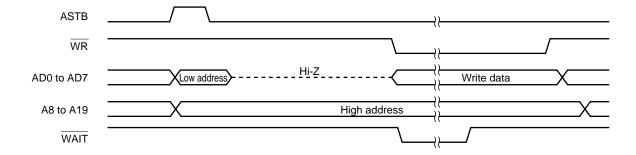

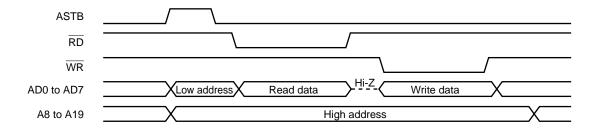

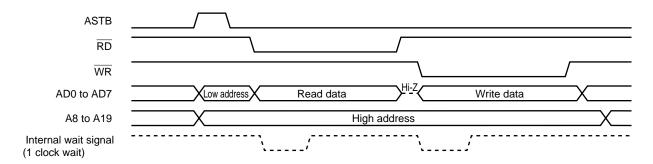

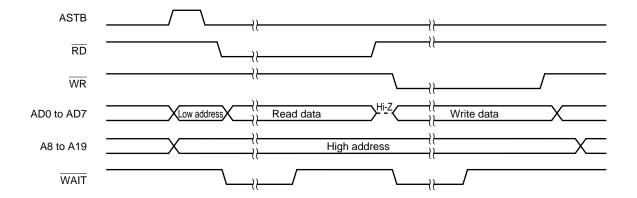

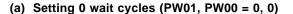

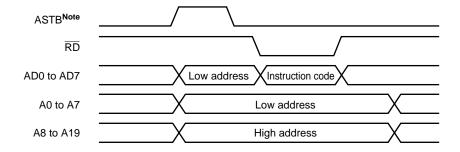

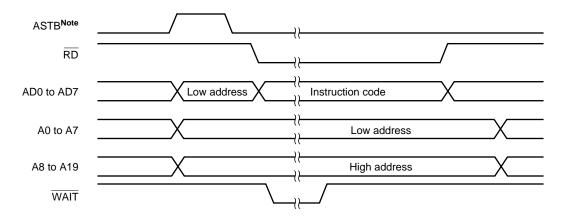

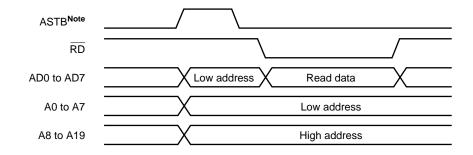

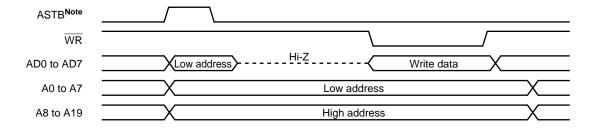

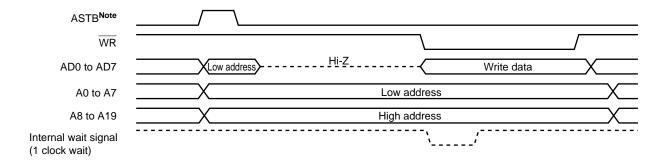

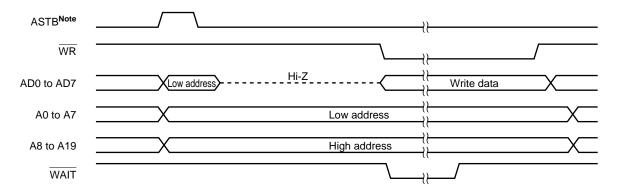

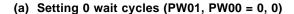

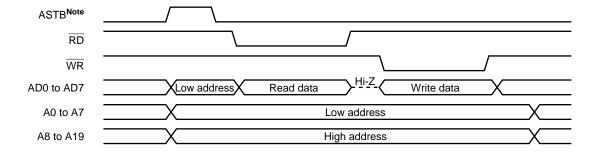

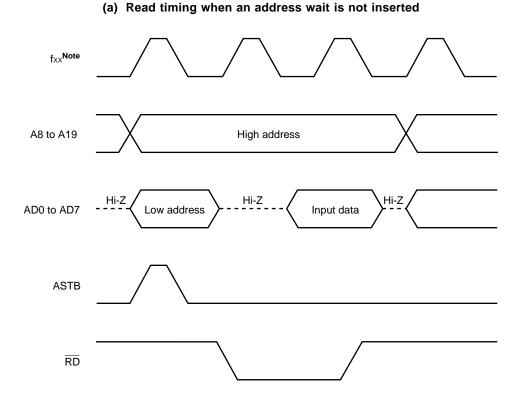

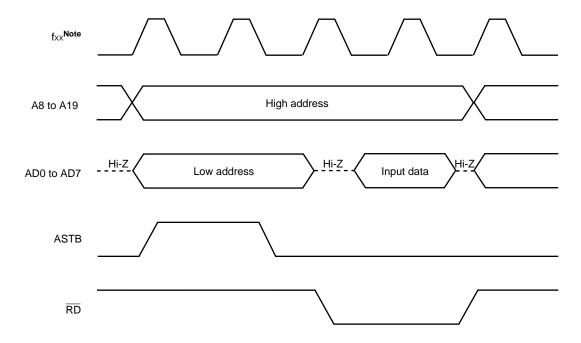

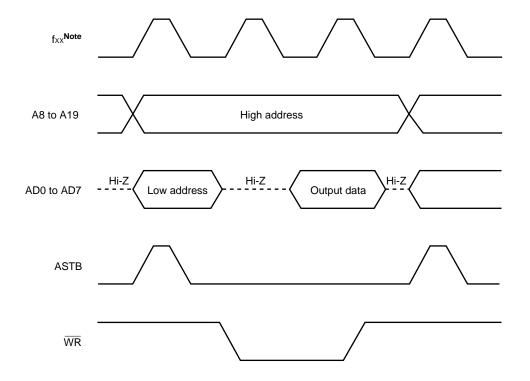

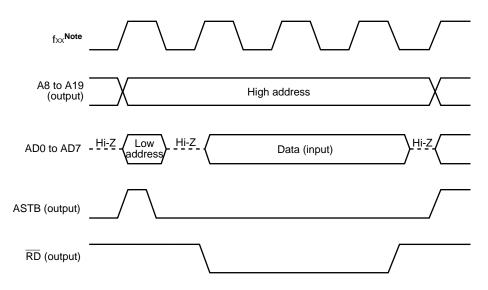

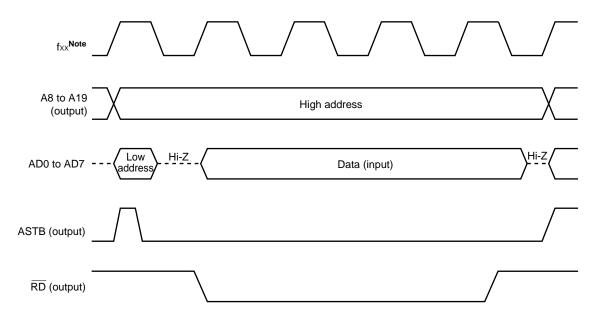

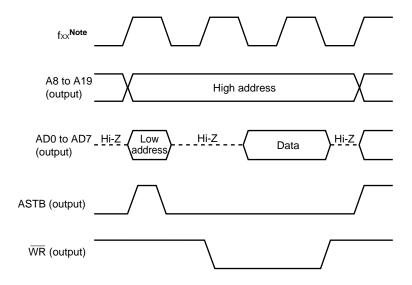

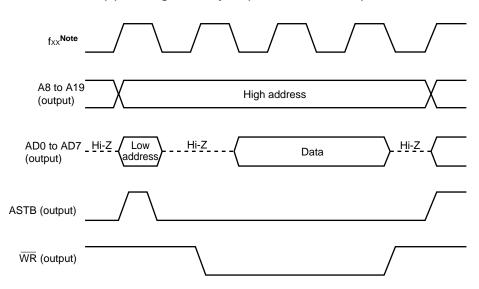

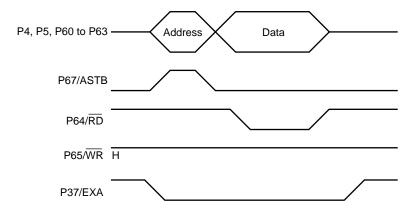

|          | 24.4.1  | Multiplexed bus mode timing                                      | 486 |

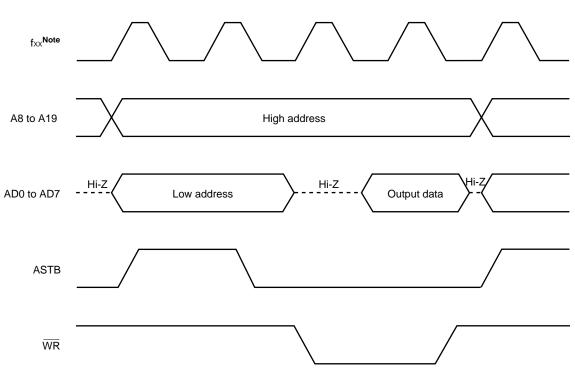

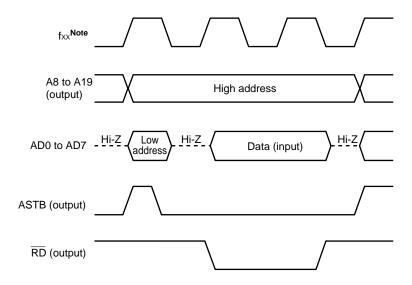

|          | 24.4.2  | Separate bus mode timing                                         | 491 |

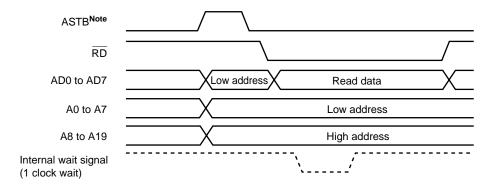

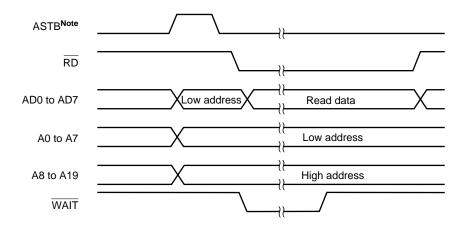

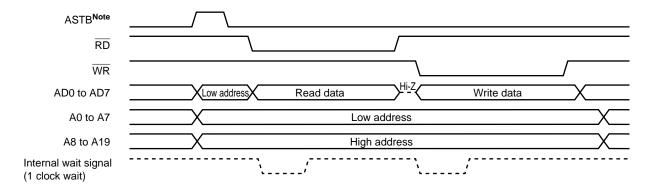

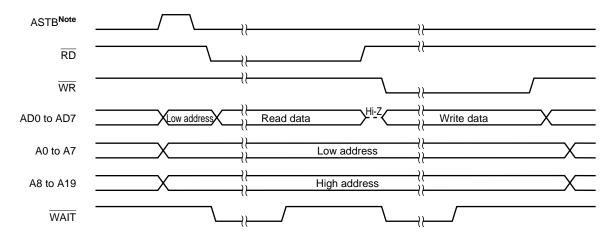

| 24.5     | Wait Fu | unctions                                                         | 496 |

|          | 24.5.1  | Address wait                                                     | 496 |

|          | 24.5.2  | Access wait                                                      | 499 |

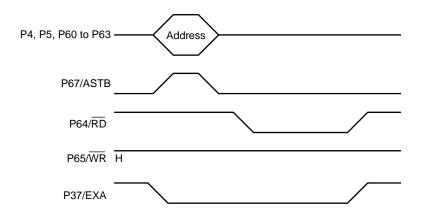

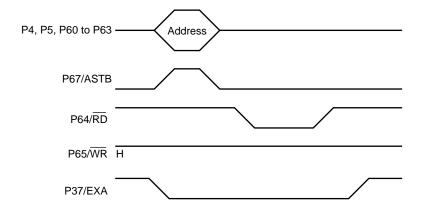

| 24.6     | Externa | al Access Status Output Function                                 | 505 |

|          | 24.6.1  | Overview                                                         | 505 |

|          | 24.6.2  | Configuration of external access status output function          | 505 |

|          | 24.6.3  | External access status enable register                           | 506 |

|          | 24.6.4  | External access status signal timing                             | 506 |

|          | 24.6.5  | EXA pin status during each mode                                  | 507 |

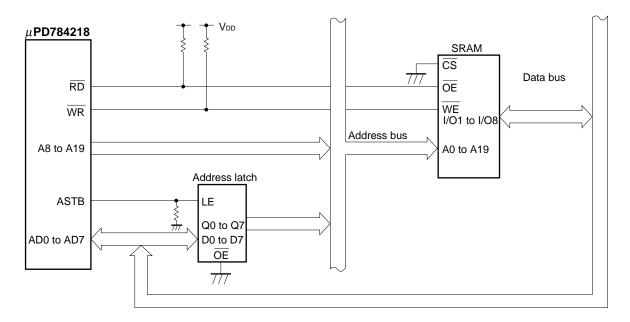

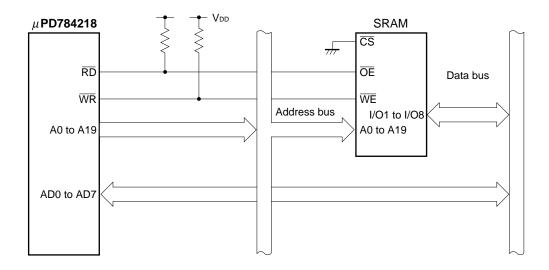

| 24.7     | Extern  | al Memory Connection Example                                     | 508 |

| CHAPT    | ER 25   | STANDBY FUNCTION                                                 | 509 |

|          |         |                                                                  |     |

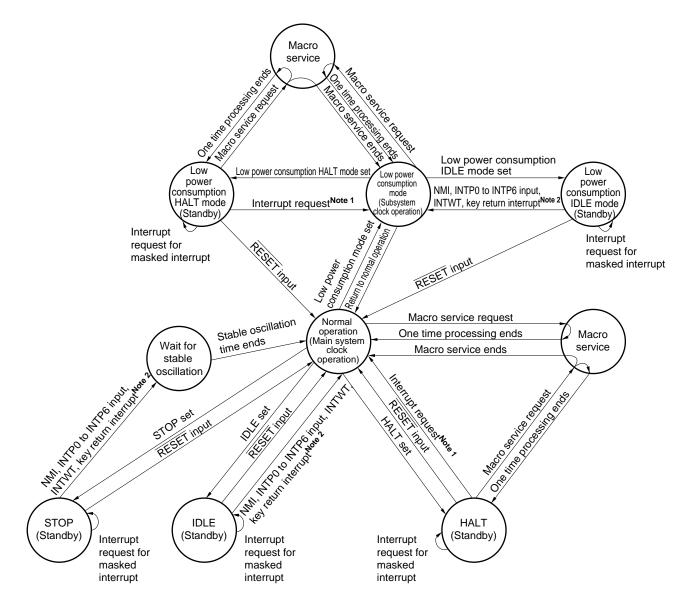

| 25.1     | Config  | uration and Function                                             | 509 |

| 25.2     | Contro  | l Registers                                                      | 511 |

| 25.3     | HALT I  | Mode                                                             | 517 |

|          | 25.3.1  | Settings and operating states of HALT mode                       | 517 |

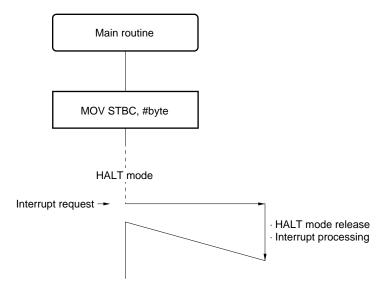

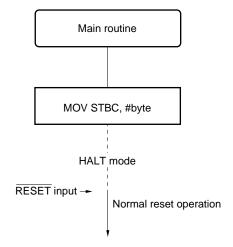

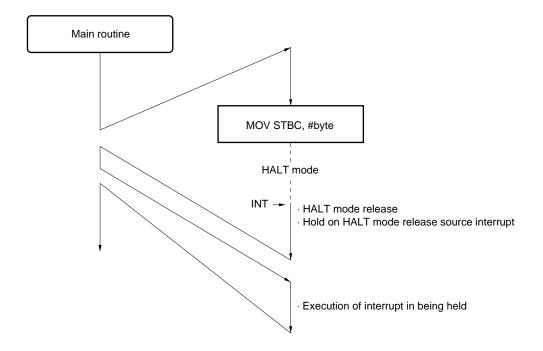

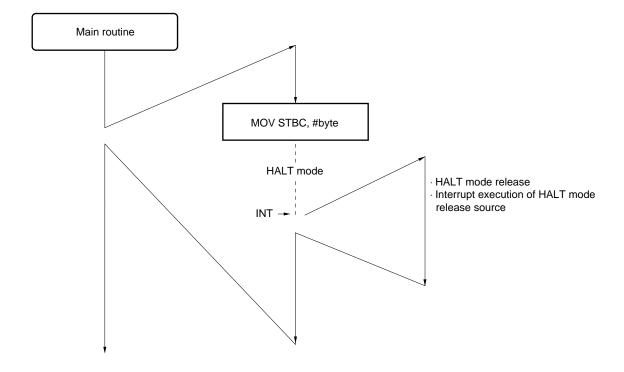

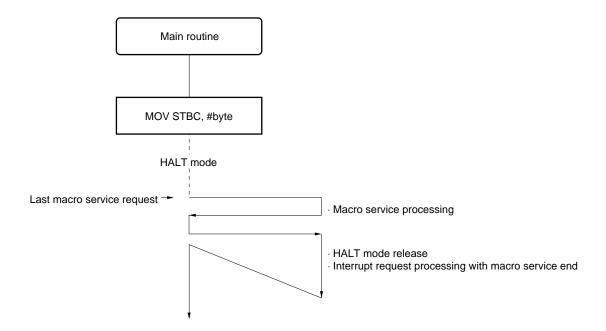

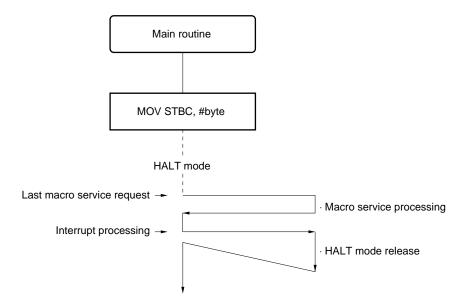

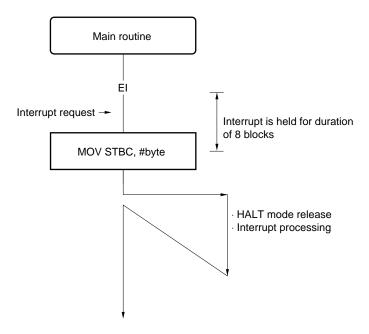

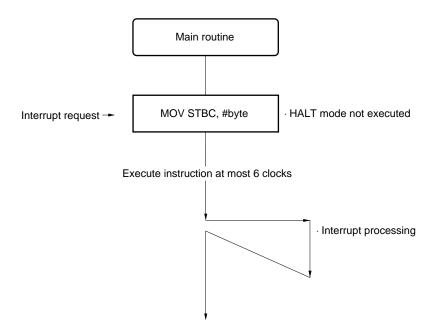

|          | 25.3.2  | Releasing HALT mode                                              | 519 |

| 25.4     | STOP    | Mode                                                             | 527 |

|          | 25.4.1  | Settings and operating states of STOP mode                       | 527 |

|          | 25.4.2  | Releasing STOP mode                                              | 529 |

| 25.5     | IDLE M  | ode                                                              | 534 |

|          | 25.5.1  | Settings and operating states of IDLE mode                       |     |

|          | 25.5.2  | Releasing IDLE mode                                              |     |

| 25.6     | Check   | Items When Using STOP or IDLE Mode                               |     |

| 25.7     |         | ower Consumption Mode                                            |     |

|          | 25.7.1  | Setting low power consumption mode                               |     |

|          | 25.7.2  | Returning to main system clock operation                         |     |

|          | 25.7.3  | Standby function in low power consumption mode                   |     |

|          | _50     |                                                                  |     |

| ~LL A DT | ER 26   | RESET FUNCTION                                                   | 551 |

| CHAPT | ER 27 ROM CORRECTION                                                  | 553 |

|-------|-----------------------------------------------------------------------|-----|

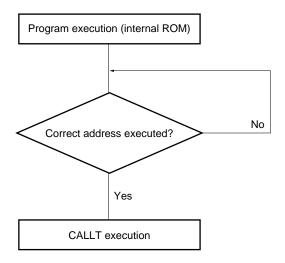

| 27.1  | ROM Correction Functions                                              | 553 |

| 27.2  | ROM Correction Configuration                                          | 555 |

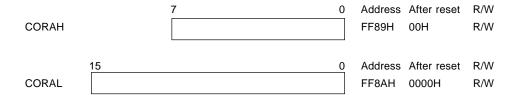

| 27.3  | Control Register for ROM Correction                                   | 557 |

| 27.4  | Usage of ROM Correction                                               | 559 |

| 27.5  | Conditions for Executing ROM Correction                               | 560 |

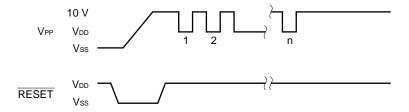

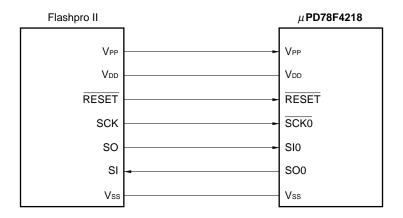

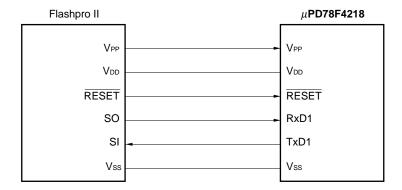

| CHAPT | ER 28 $\mu$ PD78F4218 PROGRAMMING                                     | 561 |

| 28.1  | Selecting Communication Protocol                                      | 561 |

| 28.2  | Flash Memory Programming Functions                                    | 562 |

| 28.3  | Connecting Flashpro II                                                | 563 |

| CHAPT | ER 29 INSTRUCTION OPERATION                                           | 565 |

| 29.1  | Examples                                                              |     |

| 29.2  | List of Operations                                                    | 569 |

| 29.3  | Lists of Addressing Instructions                                      | 594 |

| APPEN | DIX A MAJOR DIFFERENCES FROM $\mu$ PD78078Y SUBSERIES                 | 599 |

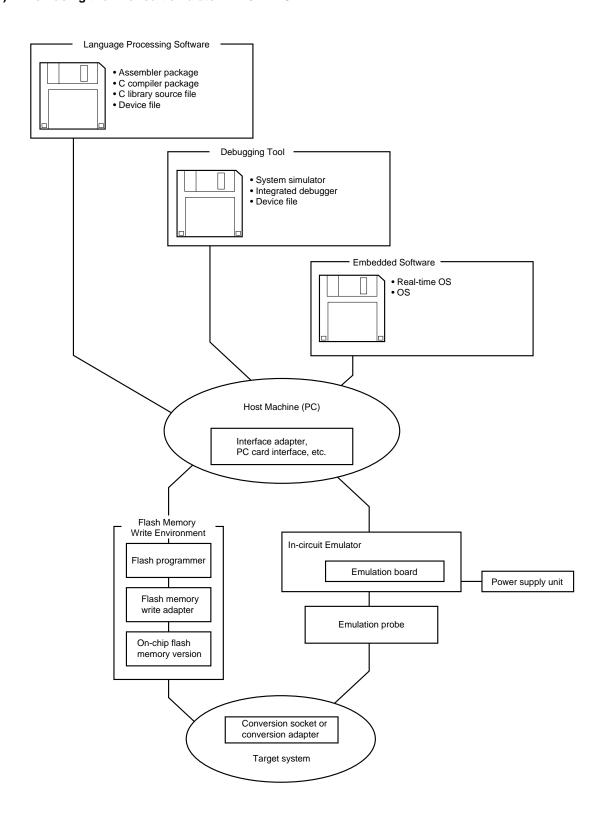

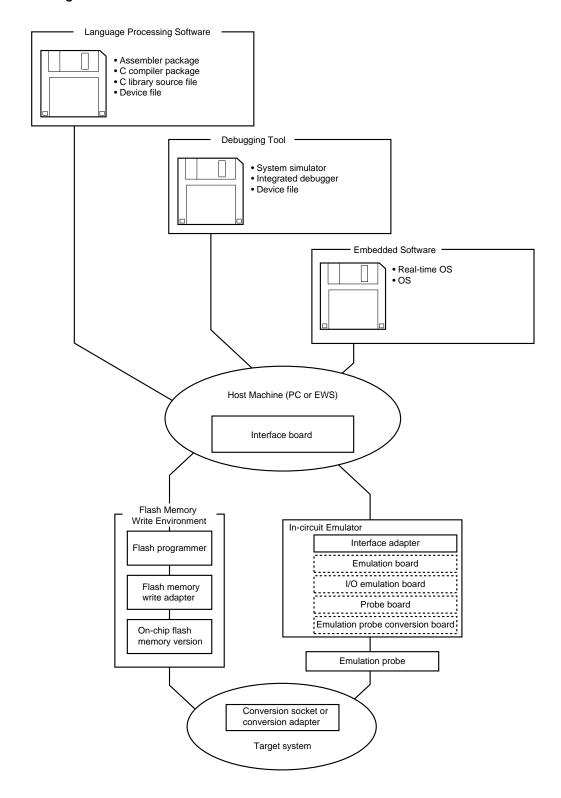

| APPEN | IDIX B DEVELOPMENT TOOLS                                              | 601 |

| B.1   | Language Processing Software                                          | 604 |

| B.2   | Flash Memory Writing Tools                                            | 605 |

| B.3   | Debugging Tools                                                       | 606 |

|       | B.3.1 Hardware                                                        | 606 |

|       | B.3.2 Software                                                        | 608 |

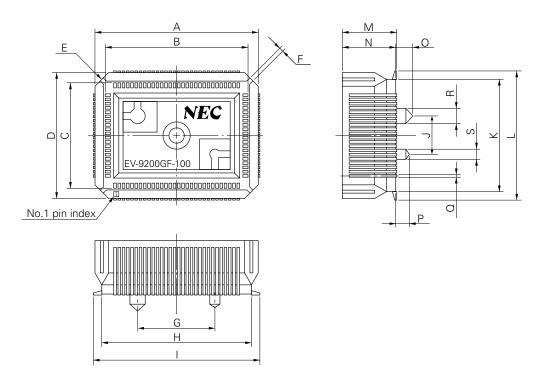

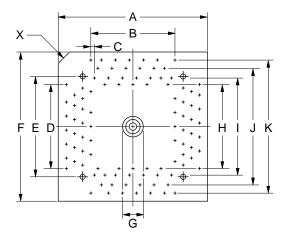

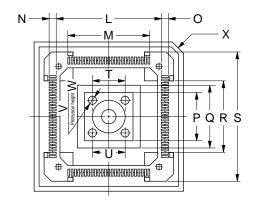

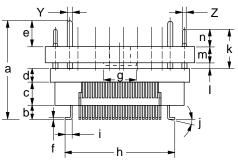

| B.4   | Conversion Socket (EV-9200GF-100) and Conversion Adapter (TGC-100SDW) | 610 |

| APPEN | DIX C EMBEDDED SOFTWARE                                               | 613 |

| APPEN | IDIX D REGISTER INDEX                                                 | 615 |

| D.1   | Register Index                                                        | 615 |

| D 2   | Register Index (Alphabetical Order)                                   | 619 |

# LIST OF FIGURES (1/8)

| Figure No | Title                                                               | Page |

|-----------|---------------------------------------------------------------------|------|

| 2-1       | Pin I/O Circuit                                                     | 60   |

| 3-1       | μPD784217 Memory Map                                                | 65   |

| 3-2       | μPD784218 Memory Map                                                | 66   |

| 3-3       | Internal RAM Memory Map                                             | 73   |

| 3-4       | Internal Memory Size Switching Register (IMS) Format                | 76   |

| 3-5       | Program Counter (PC) Format                                         | 77   |

| 3-6       | Program Status Word (PSW) Format                                    | 78   |

| 3-7       | Stack Pointer (SP) Format                                           | 84   |

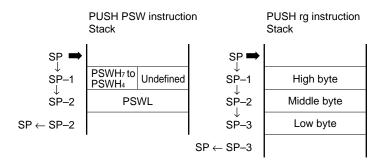

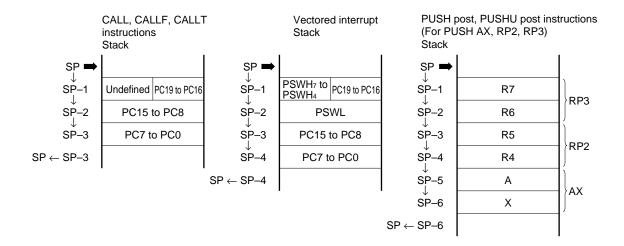

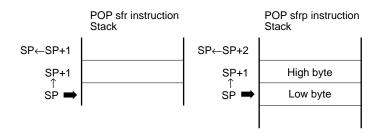

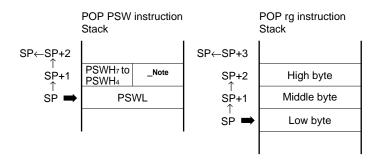

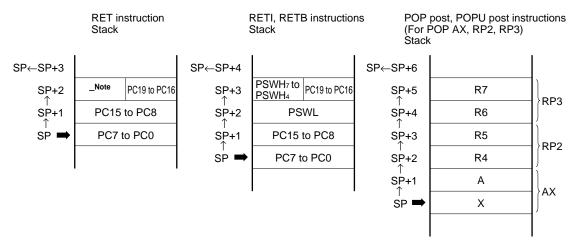

| 3-8       | Data Saved to Stack                                                 | 85   |

| 3-9       | Data Restored from Stack                                            | 86   |

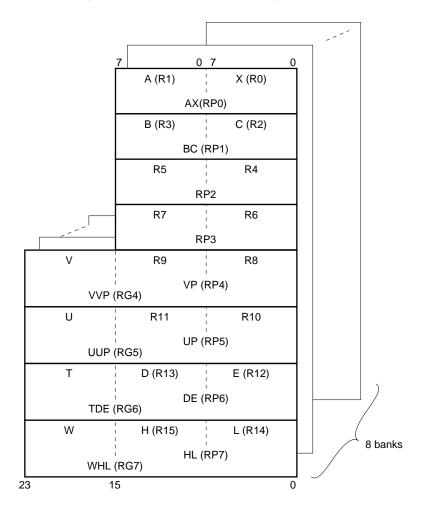

| 3-10      | General-purpose Register Format                                     | 88   |

| 3-11      | General-purpose Register Addresses                                  | 89   |

| 4-1       | Block Diagram of Clock Generator                                    | 102  |

| 4-2       | Standby Control Register (STBC) Format                              | 104  |

| 4-3       | Oscillation Mode Selection Register (CC) Format                     | 105  |

| 4-4       | Clock Status Register (PCS) Format                                  | 106  |

| 4-5       | Oscillation Stabilization Time Specification Register (OSTS) Format | 107  |

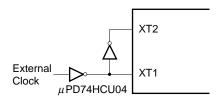

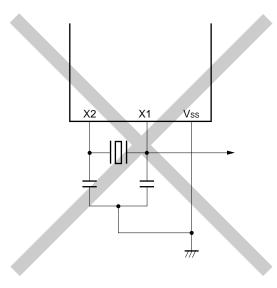

| 4-6       | External Circuit of Main System Clock Oscillator                    | 108  |

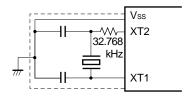

| 4-7       | External Circuit of Subsystem Clock Oscillator                      | 109  |

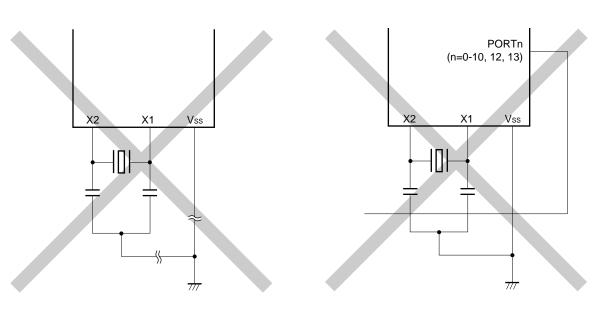

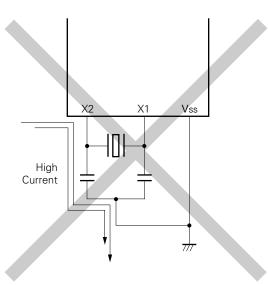

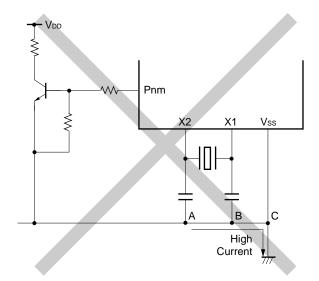

| 4-8       | Examples of Oscillator Connected Incorrectly                        | 110  |

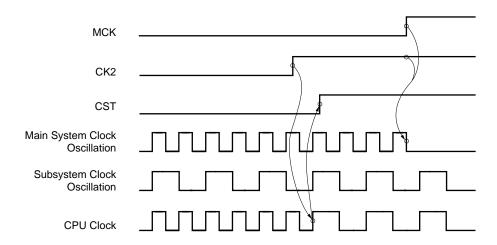

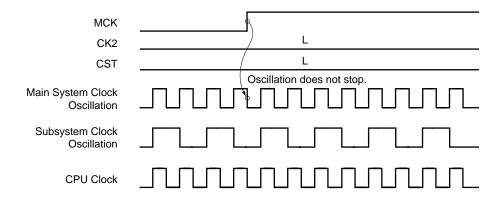

| 4-9       | Main System Clock Stop Function                                     | 114  |

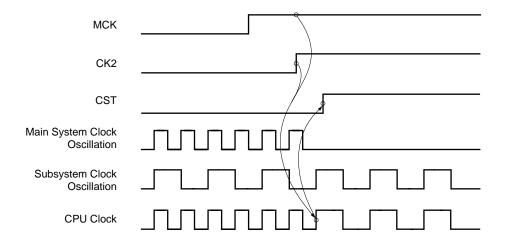

| 4-10      | System Clock and CPU Clock Switching                                | 116  |

| 5-1       | Port Configuration                                                  | 117  |

| 5-2       | Block Diagram of P00 to P06                                         | 120  |

| 5-3       | Block Diagram of P10 to P17                                         | 121  |

| 5-4       | Block Diagram of P20 to P24 and P26                                 | 122  |

| 5-5       | Block Diagram of P25 and P27                                        | 123  |

| 5-6       | Block Diagram of P30 to P37                                         | 124  |

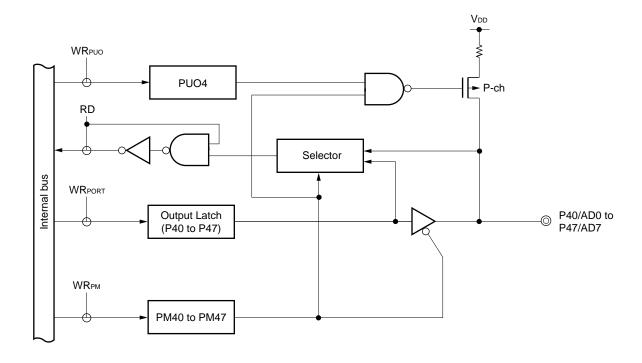

| 5-7       | Block Diagram of P40 to P47                                         | 125  |

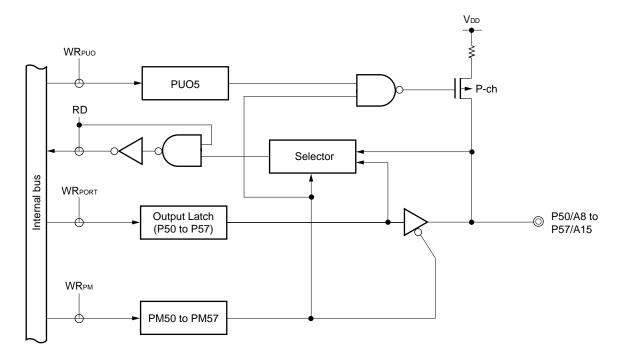

| 5-8       | Block Diagram of P50 to P57                                         | 126  |

| 5-9       | Block Diagram of P60 to P63                                         | 127  |

| 5-10      | Block Diagram of P64 to P67                                         | 128  |

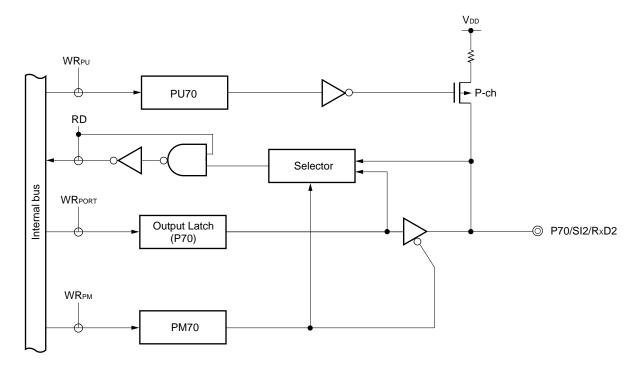

| 5-11      | Block Diagram of P70                                                | 129  |

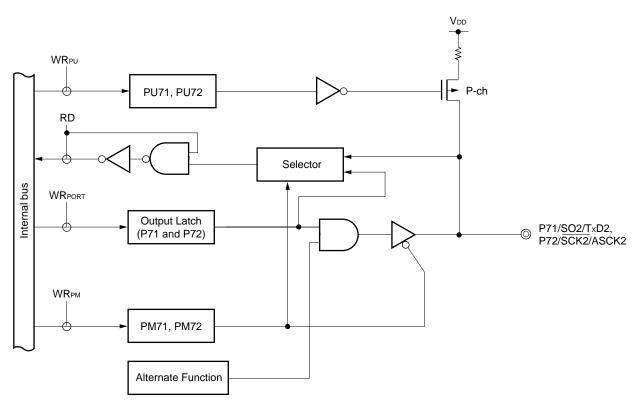

| 5-12      | Block Diagram of P71 and P72                                        | 130  |

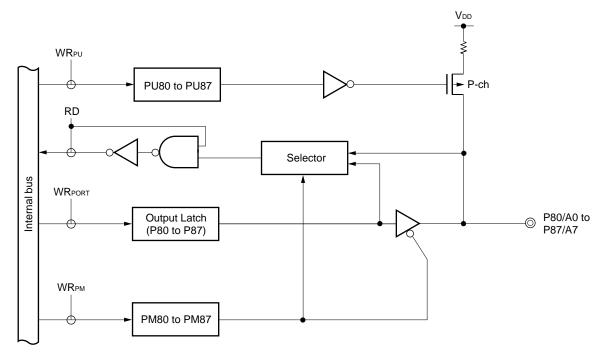

| 5-13      | Block Diagram of P80 to P87                                         | 131  |

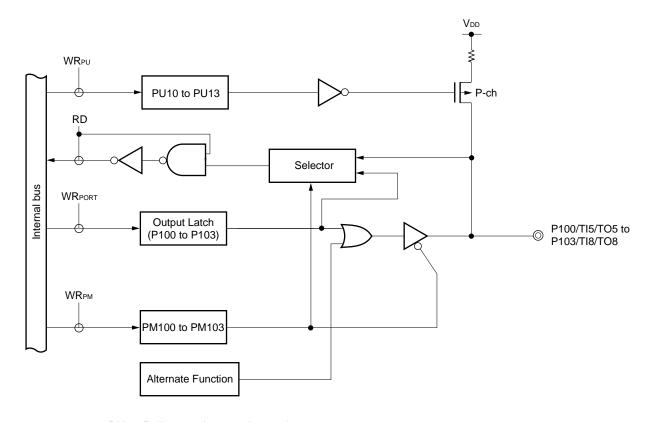

| 5-14      | Block Diagram of Falling Edge Detection Circuit                     | 131  |

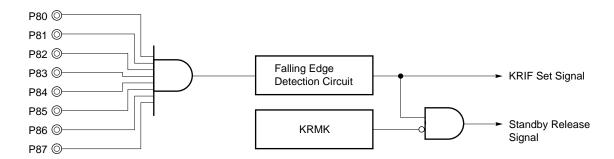

| 5-15      | Block Diagram of P90 to P95                                         | 132  |

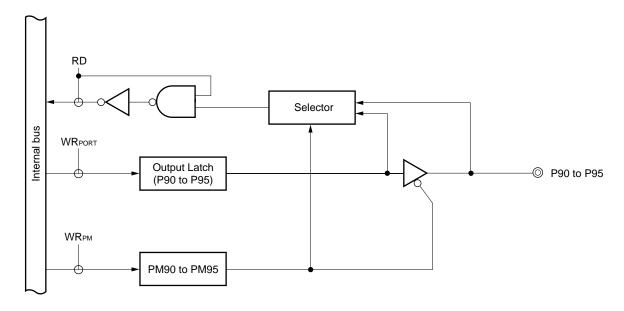

| 5-16      | Block Diagram of P100 to P103                                       | 133  |

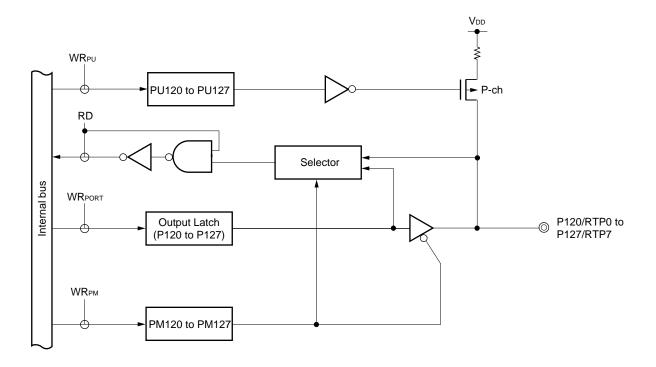

| 5-17      | Block Diagram of P120 to P127                                       |      |

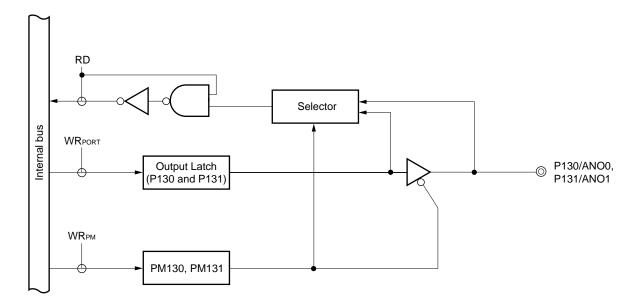

| 5-18      | Block Diagram of P130 and P131                                      | 135  |

# LIST OF FIGURES (2/8)

| Figure No. | Title                                                                                                              | Page |

|------------|--------------------------------------------------------------------------------------------------------------------|------|

| 5-19       | Port Mode Register Format                                                                                          | 138  |

| 5-20       | Pull-Up Resistor Option Register Format                                                                            |      |

| 5-21       | Port Function Control Register (PF2) Format                                                                        |      |

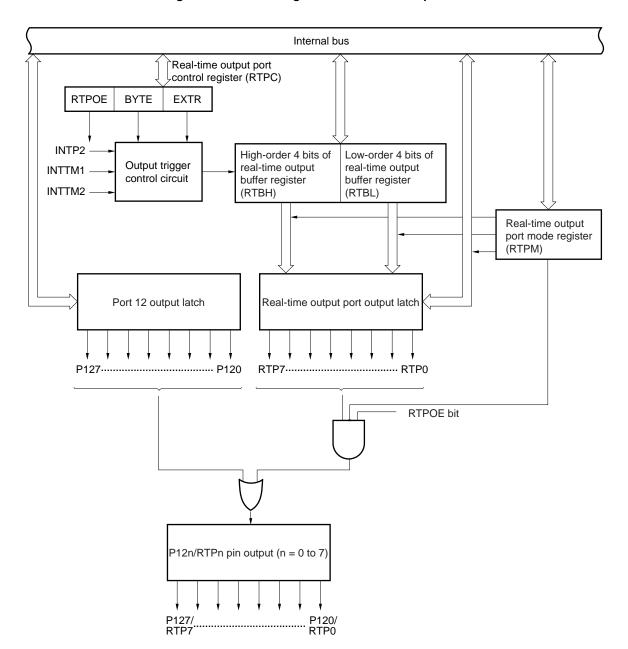

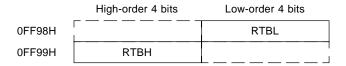

| 6-1        | Block Diagram of Real-time Output Port                                                                             | 146  |

| 6-2        | Real-time Output Buffer Register Configuration                                                                     | 147  |

| 6-3        | Real-time Output Port Mode Register (RTPM) Format                                                                  | 148  |

| 6-4        | Real-time Output Port Control Register (RTPC) Format                                                               | 149  |

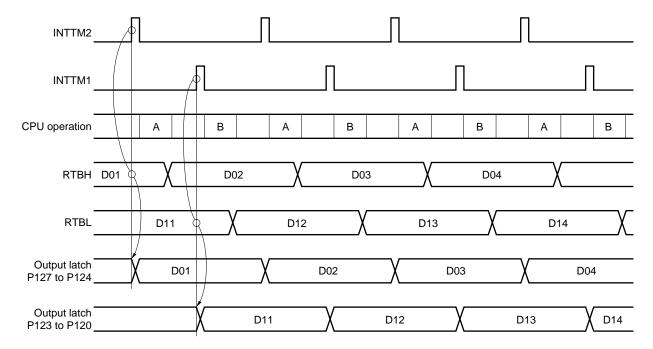

| 6-5        | Example of Operation Timing of Real-time Output Port (EXTR = 0, BYTE = 0)                                          | 150  |

| 7-1        | Timer/Counter Block Diagram                                                                                        | 154  |

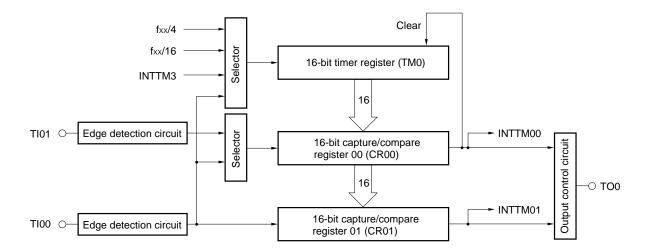

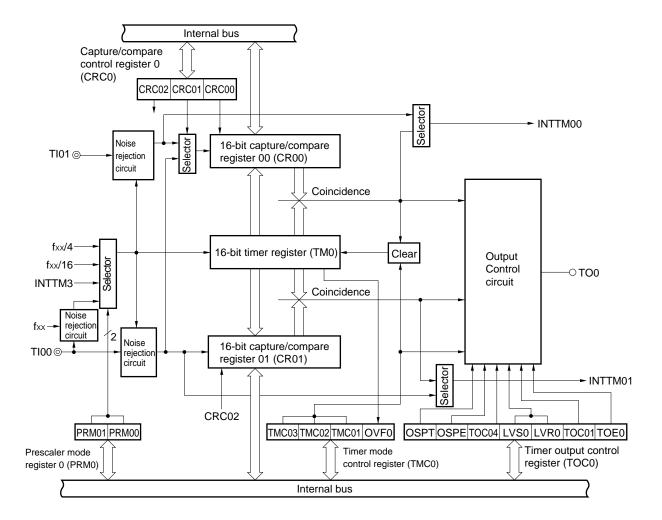

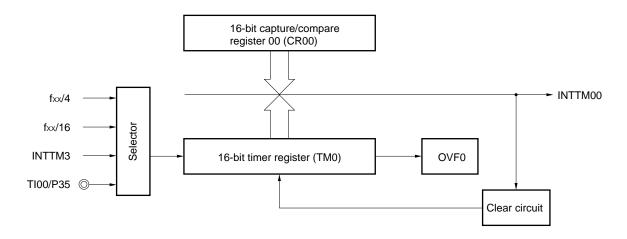

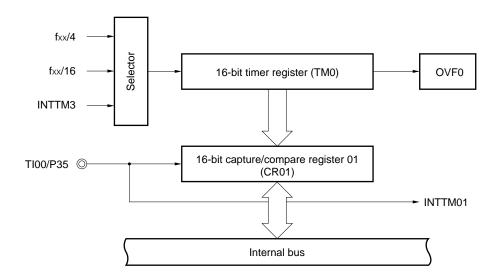

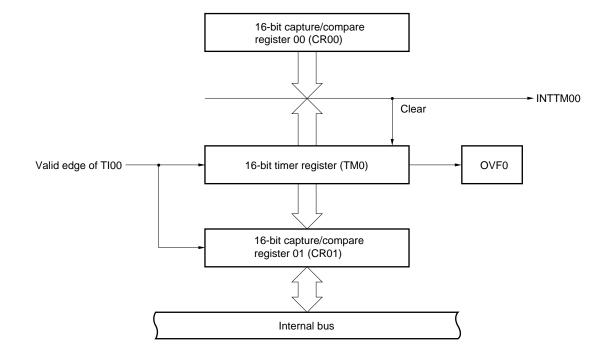

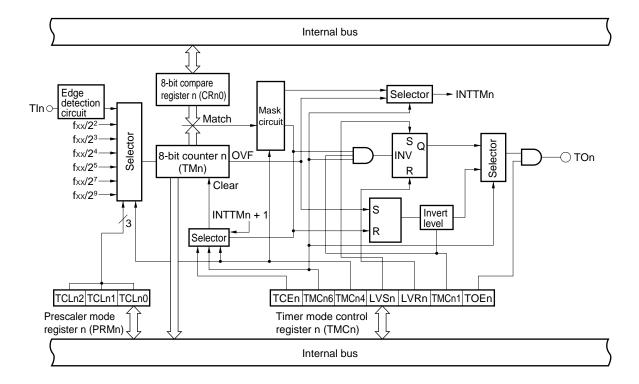

| 8-1        | Block Diagram of 16-Bit Timer/Counter (TM0)                                                                        | 158  |

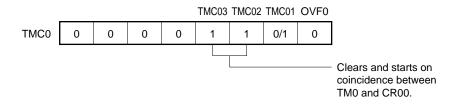

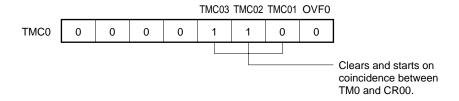

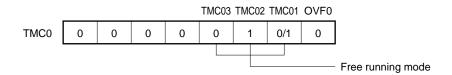

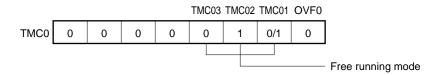

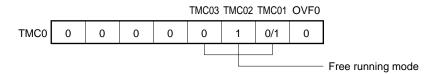

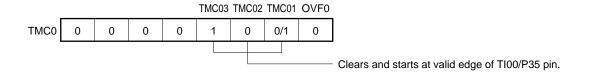

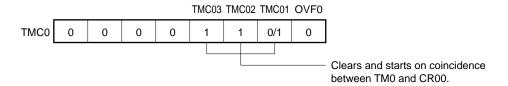

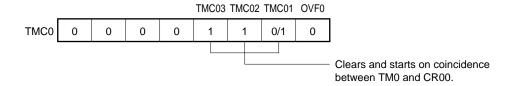

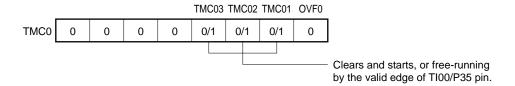

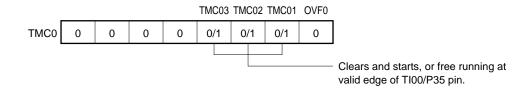

| 8-2        | Format of 16-Bit Timer Mode Control Register (TMC0)                                                                | 163  |

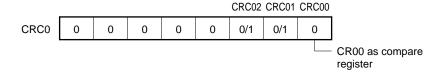

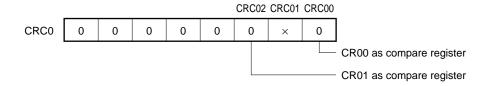

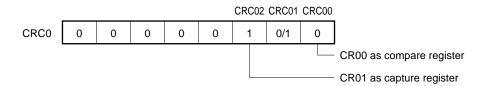

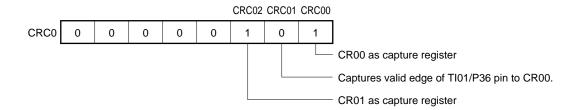

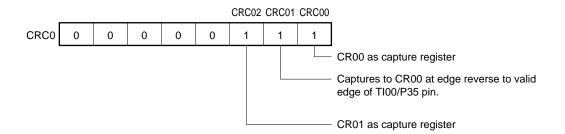

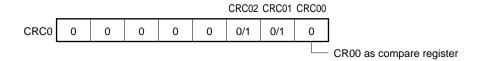

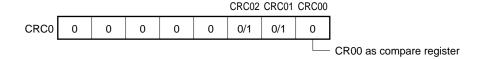

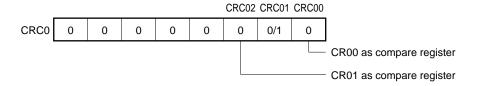

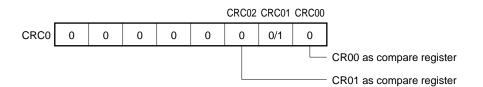

| 8-3        | Format of Capture/Compare Control Register 0 (CRC0)                                                                | 165  |

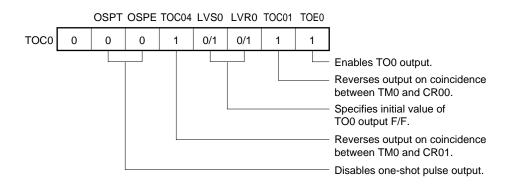

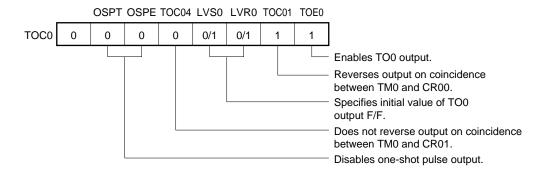

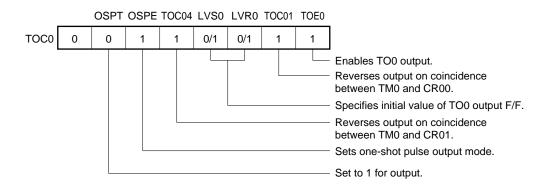

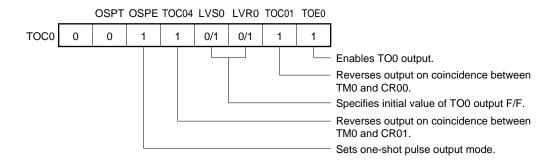

| 8-4        | Format of 16-Bit Timer Output Control Register (TOC0)                                                              | 166  |

| 8-5        | Format of Prescaler Mode Register 0 (PRM0)                                                                         | 167  |

| 8-6        | Control Register Settings during Interval Timer Operation                                                          | 168  |

| 8-7        | Configuration of Interval Timer                                                                                    | 169  |

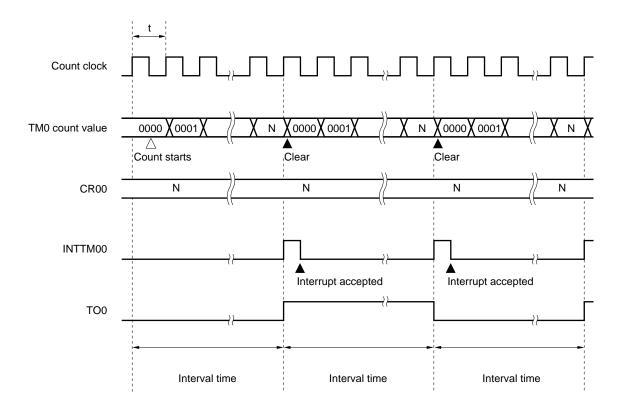

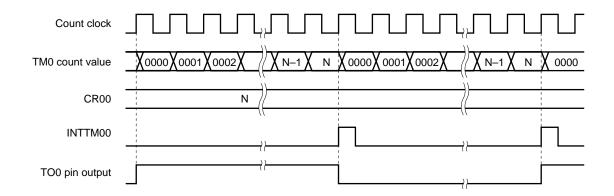

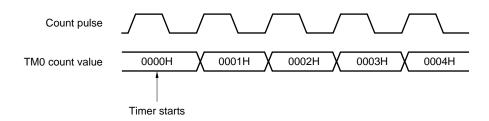

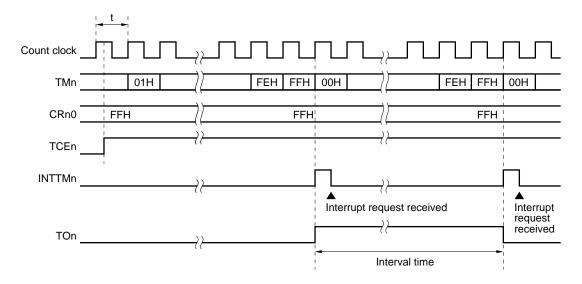

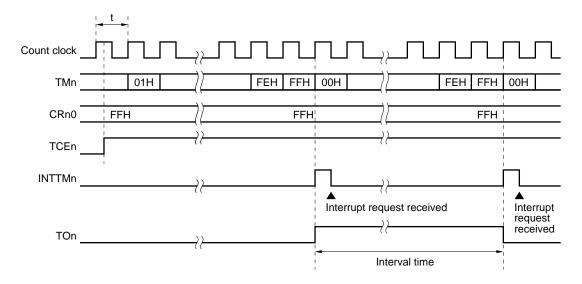

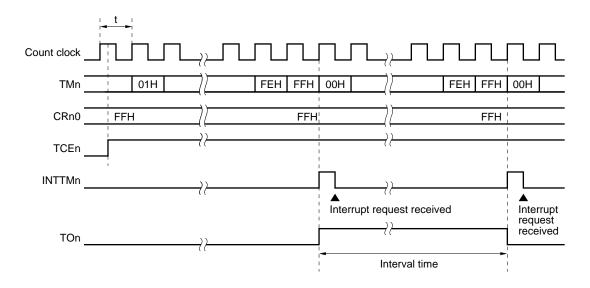

| 8-8        | Timing of Interval Timer Operation                                                                                 | 169  |

| 8-9        | Control Register Settings during PPG Output Operation                                                              | 170  |

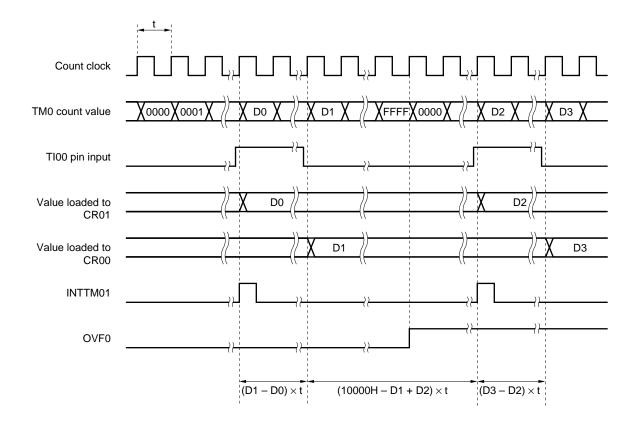

| 8-10       | Control Register Settings during Pulse Width Measurement with                                                      |      |

|            | Free Running Counter and One Capture Register                                                                      | 171  |

| 8-11       | Configuration for Pulse Width Measurement with Free Running Counter                                                | 172  |

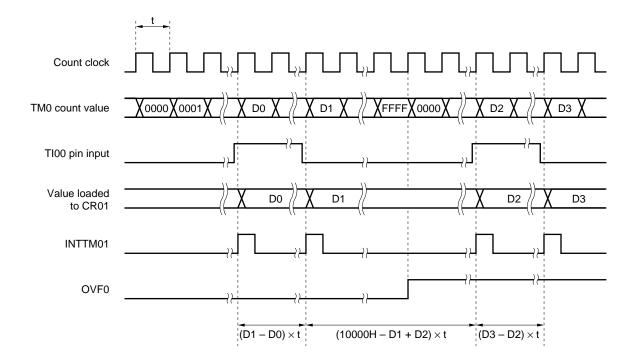

| 8-12       | Timing of Pulse Width Measurement with Free Running Counter and One Capture Register (with both edges specified)   | 172  |

| 8-13       | Control Register Settings during Measurement of Two Pulse Widths with Free Running Counter                         |      |

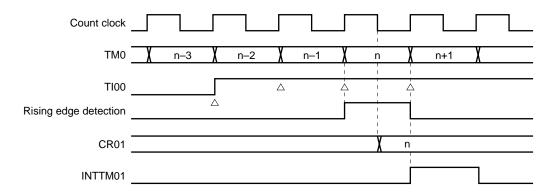

| 8-14       | CR01 Capture Operation with Rising Edge Specified                                                                  |      |

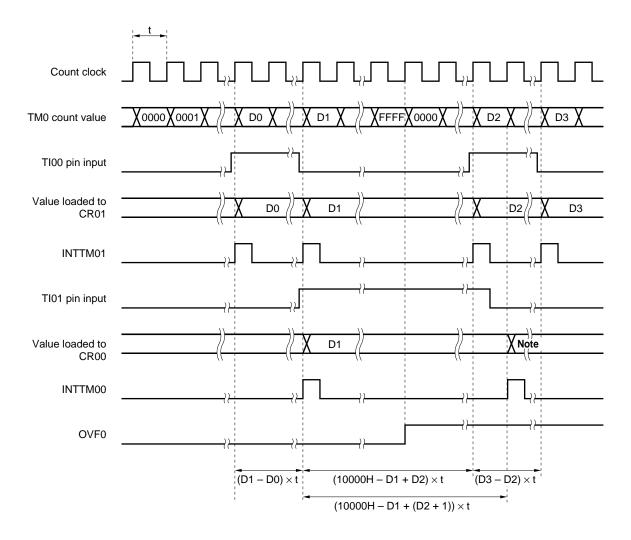

| 8-15       | Timing of Pulse Width Measurement with Free Running Counter (with both edges specified)                            |      |

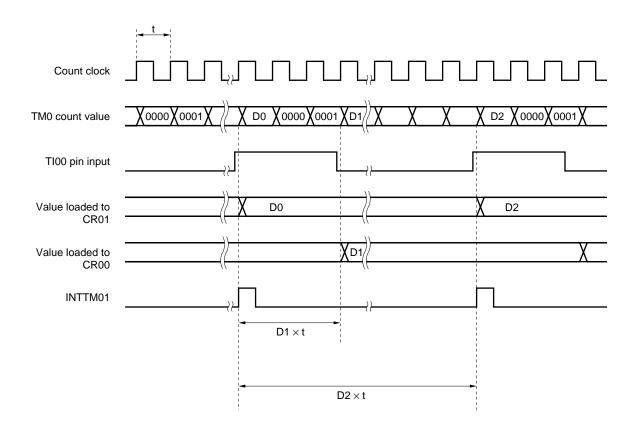

| 8-16       | Control Register Settings during Pulse Width Measurement with Free Running Counter and Two Capture Registers       |      |

| 8-17       | Timing of Pulse Width Measurement with Free Running Counter and Two Capture Registers (with rising edge specified) |      |

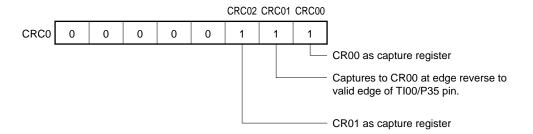

| 8-18       | Control Register Settings during Pulse Width Measurement by Restarting                                             |      |

| 8-19       | Timing of Pulse Width Measurement by Restarting (with rising edge specified)                                       |      |

| 8-20       | Control Register Settings during External Event Counter Mode                                                       |      |

| 8-21       | Configuration of External Event Counter                                                                            |      |

| 8-22       | Timing of External Event Counter Operation (with rising edge specified)                                            |      |

| 8-23       | Control Register Settings during Square Wave Output Mode                                                           |      |

| 8-24       | Timing of Square Wave Output Operation                                                                             |      |

| 8-25       | Control Register Settings during One-Shot Pulse Output with Software Trigger                                       |      |

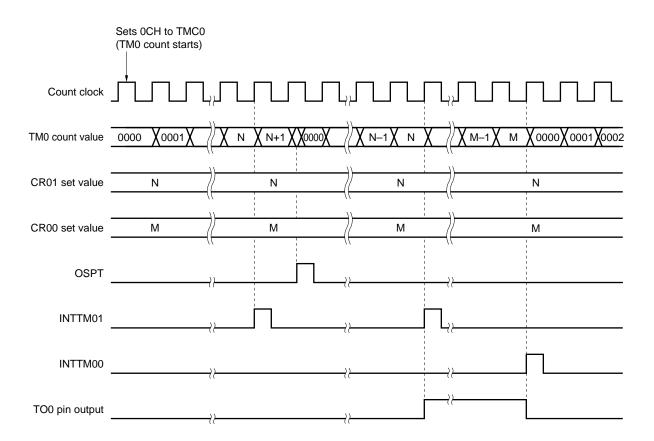

| 8-26       | Timing of One-Shot Pulse Output Operation with Software Trigger                                                    |      |

| 8-27       | Control Register Settings during One-Shot Pulse Output with External Trigger                                       |      |

| 8-28       | Timing of One-Shot Pulse Output Operation with External Trigger (with rising edge specified)                       |      |

|            | 5                                                                                                                  |      |

# LIST OF FIGURES (3/8)

| Figure No. | Title                                                                        | Page |

|------------|------------------------------------------------------------------------------|------|

| 8-29       | Start Timing of 16-Bit Timer Register                                        | 187  |

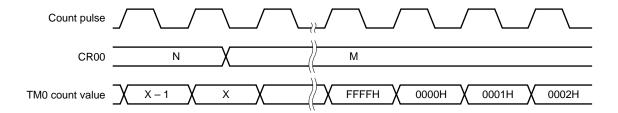

| 8-30       | Timing after Changing Value of Compare Register during Timer Count Operation |      |

| 8-31       | Data Hold Timing of Capture Register                                         |      |

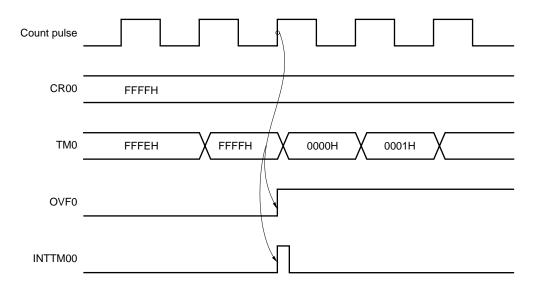

| 8-32       | Operation Timing of OVF0 Flag                                                |      |

| 0 02       | Opolation Tilling of CVT CT lag                                              |      |

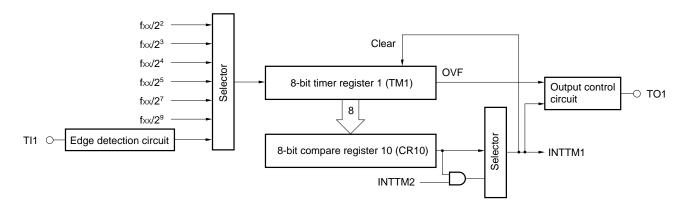

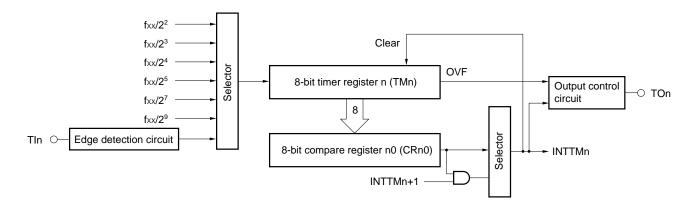

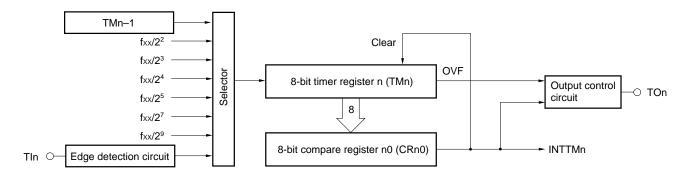

| 9-1        | Block Diagram of 8-bit Timer/Counter 1, 2                                    | 192  |

| 9-2        | Format of 8-Bit Timer Mode Control Register 1 (TMC1)                         | 195  |

| 9-3        | Format of 8-Bit Timer Mode Control Register 2 (TMC2)                         | 196  |

| 9-4        | Format of Prescaler Mode Register 1 (PRM1)                                   | 197  |

| 9-5        | Format of Prescaler Mode Register 2 (PRM2)                                   | 198  |

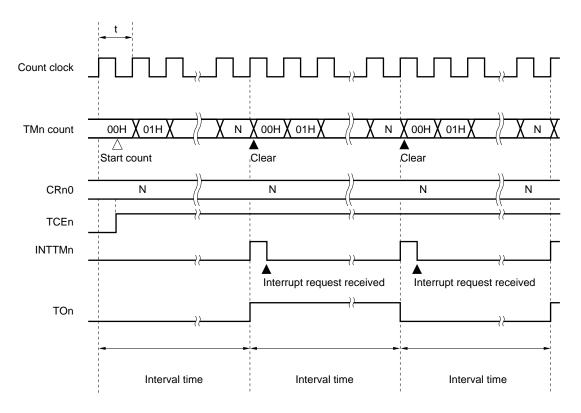

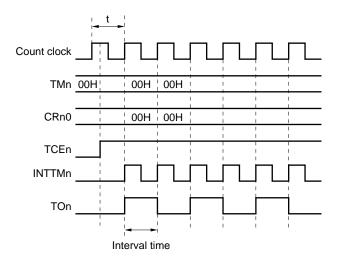

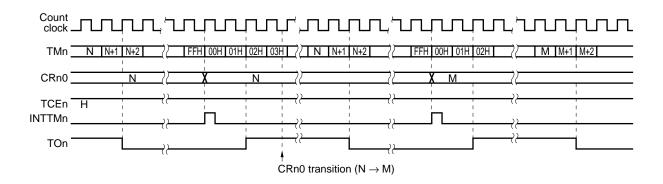

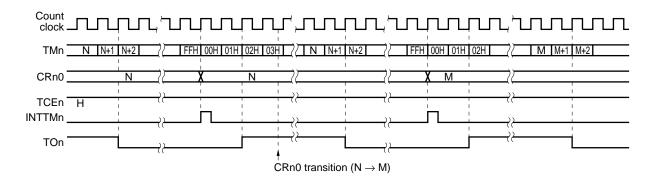

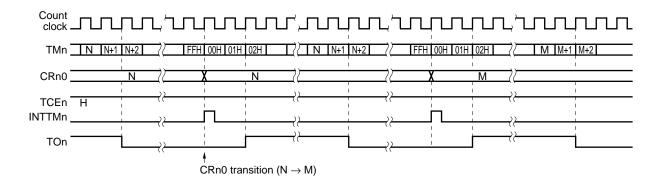

| 9-6        | Timing of Interval Timer Operation                                           | 200  |

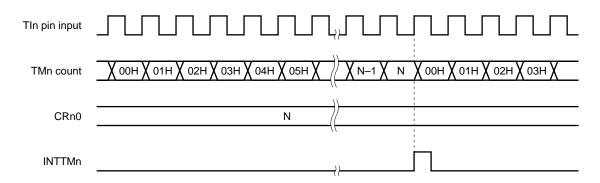

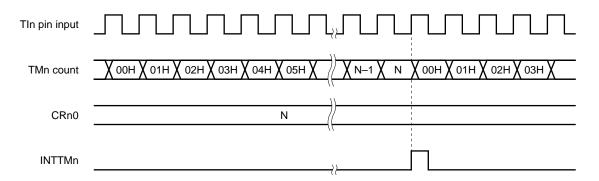

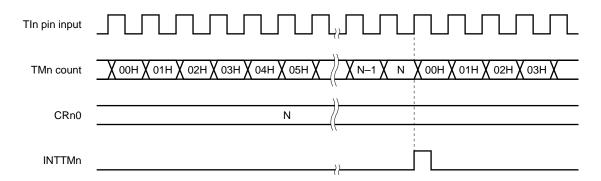

| 9-7        | Timing of External Event Counter Operation (with rising edge specified)      | 203  |

| 9-8        | Timing of PWM Output                                                         | 206  |

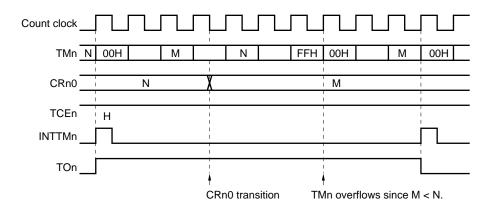

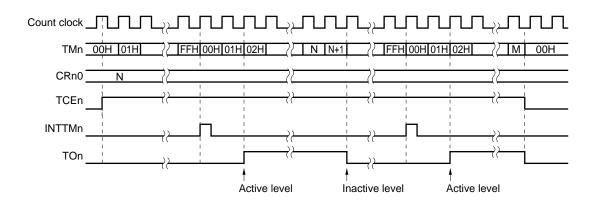

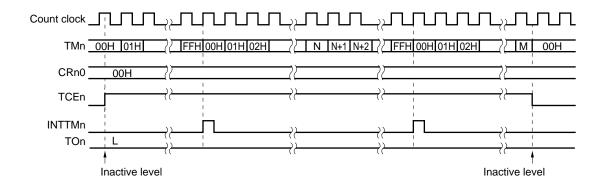

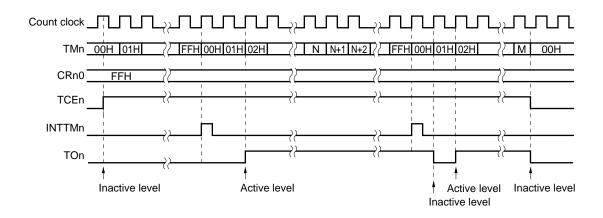

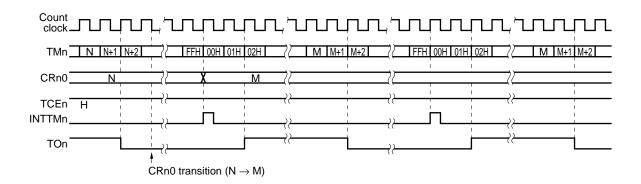

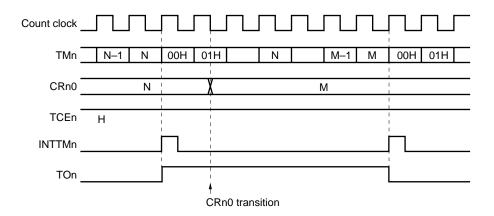

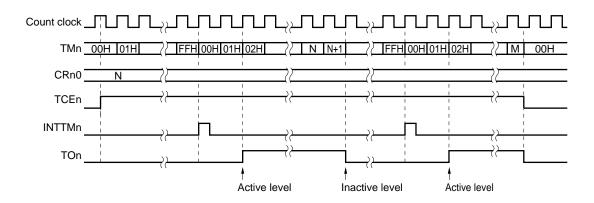

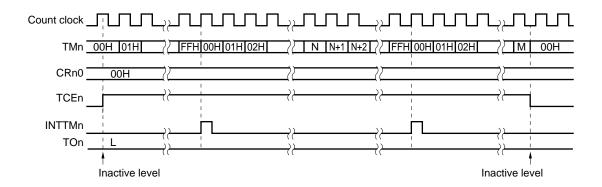

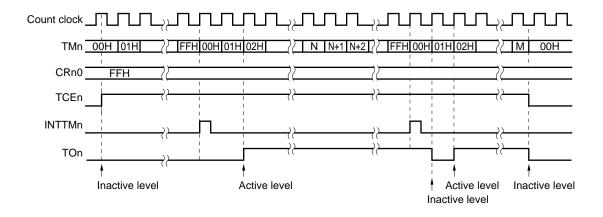

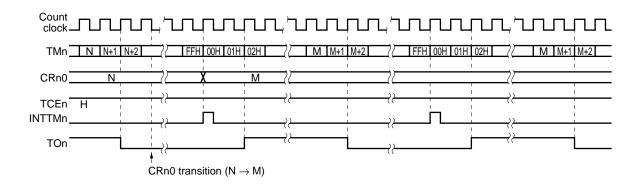

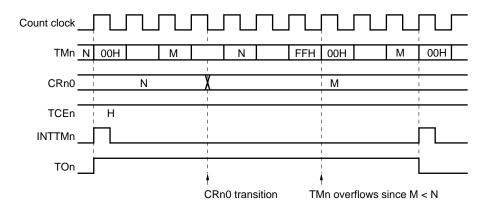

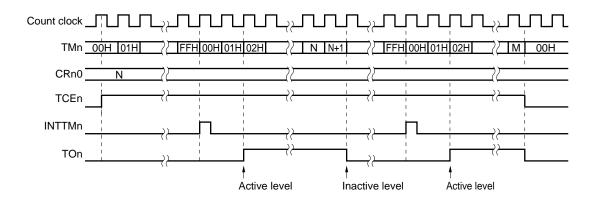

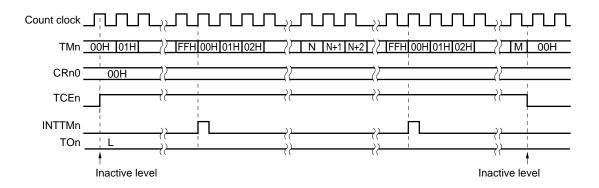

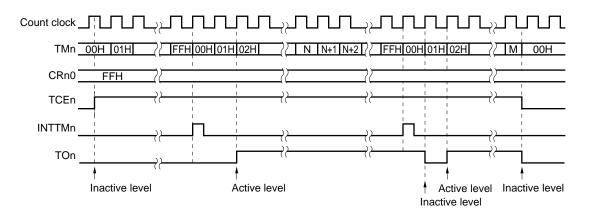

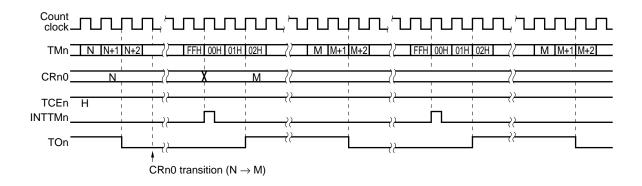

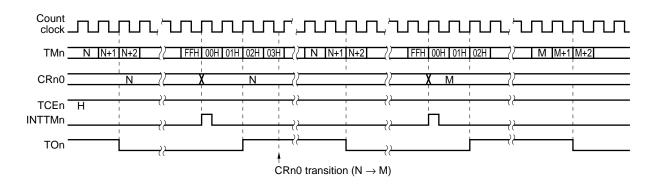

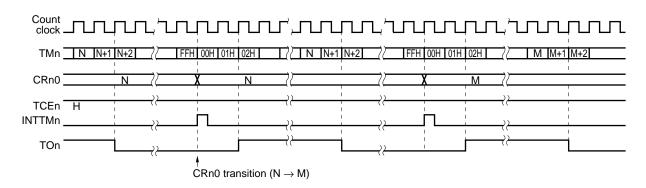

| 9-9        | Timing of Operation Based on CRn0 Transitions                                | 207  |

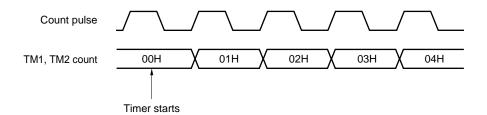

| 9-10       | Cascade Connection Mode with 16-Bit Resolution                               | 209  |

| 9-11       | Start Timing of 8-Bit Timer Register                                         | 209  |

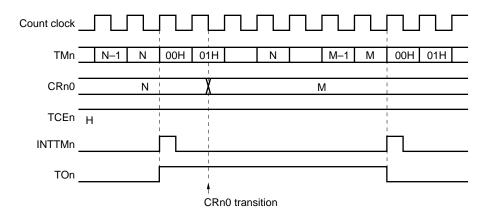

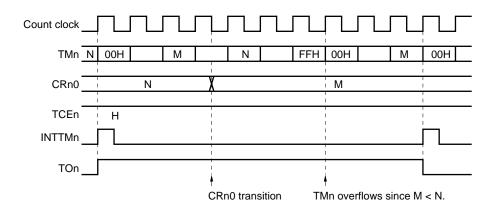

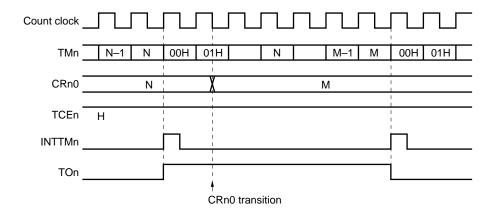

| 9-12       | Timing After Compare Register Changes During Timer Counting                  | 210  |

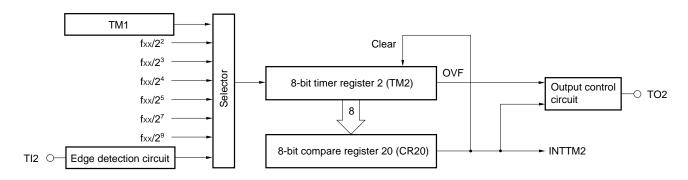

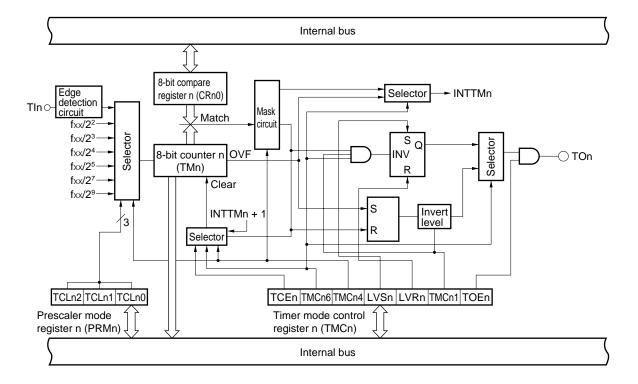

| 10-1       | Block Diagram of 8-bit Timer/Counter 5, 6                                    | 212  |

| 10-2       | Format of 8-Bit Timer Mode Control Register 5 (TMC5)                         | 215  |

| 10-3       | Format of 8-Bit Timer Mode Control Register 6 (TMC6)                         | 216  |

| 10-4       | Format of Prescaler Mode Register 5 (PRM5)                                   | 217  |

| 10-5       | Format of Prescaler Mode Register 6 (PRM6)                                   | 218  |

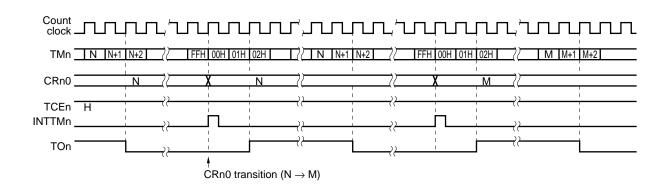

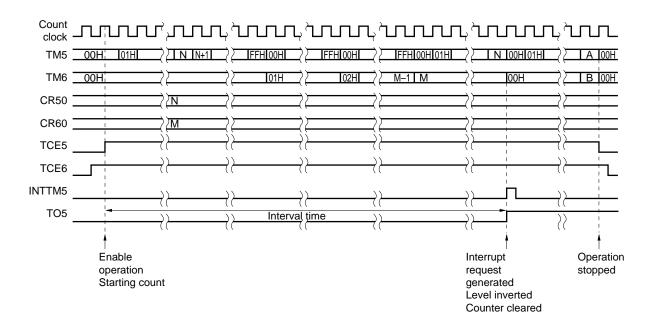

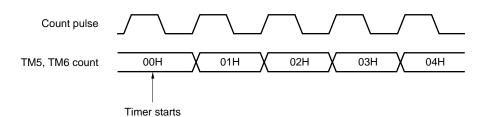

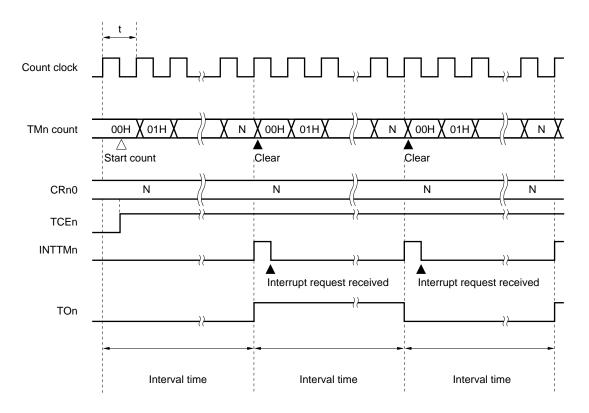

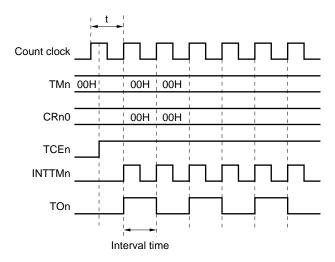

| 10-6       | Timing of Interval Timer Operation                                           | 220  |

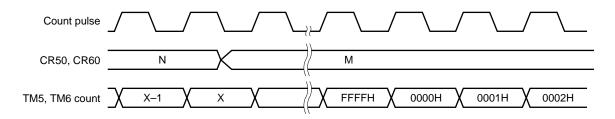

| 10-7       | Timing of External Event Counter Operation (with rising edge specified)      | 223  |

| 10-8       | Timing of PWM Output                                                         | 226  |

| 10-9       | Timing of Operation Based on CRn0 Transitions                                | 227  |

| 10-10      | Cascade Connection Mode with 16-Bit Resolution                               | 229  |

| 10-11      | Start Timing of 8-Bit Timer Register                                         | 229  |

| 10-12      | Timing After Compare Register Changes During Timer Counting                  | 230  |

| 11-1       | Block Diagram of 8-bit Timer/Counter 7, 8                                    | 232  |

| 11-2       | Format of 8-Bit Timer Mode Control Register 7 (TMC7)                         | 235  |

| 11-3       | Format of 8-Bit Timer Mode Control Register 8 (TMC8)                         | 236  |

| 11-4       | Format of Prescaler Mode Register 7 (PRM7)                                   | 237  |

| 11-5       | Format of Prescaler Mode Register 8 (PRM8)                                   | 238  |

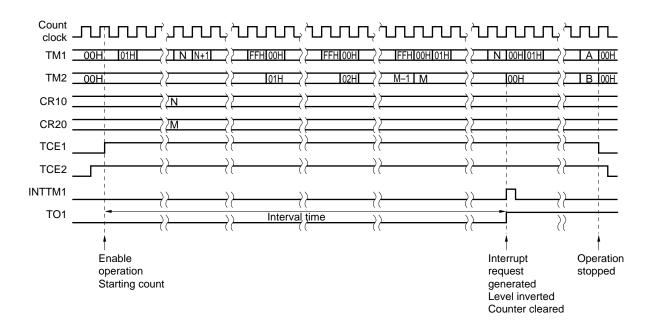

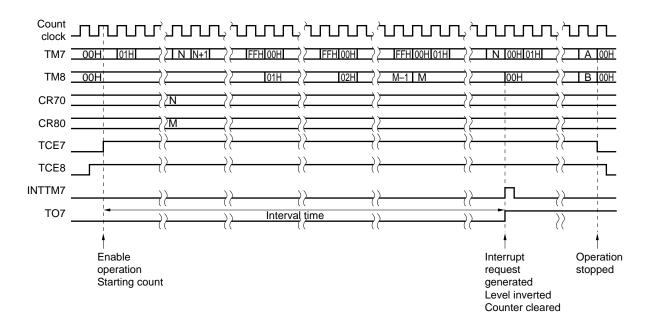

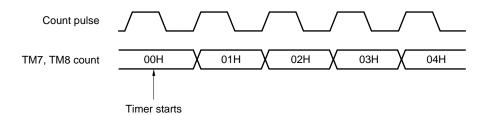

| 11-6       | Timing of Interval Timer Operation                                           | 240  |

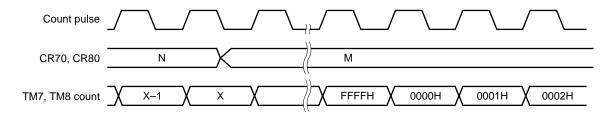

| 11-7       | Timing of External Event Counter Operation (with rising edge specified)      | 243  |

| 11-8       | Timing of PWM Output                                                         | 246  |

| 11-9       | Timing of Operation Based on CRn0 Transitions                                | 247  |

| 11-10      | Cascade Connection Mode with 16-Bit Resolution                               | 249  |

| 11-11      | Start Timing of 8-Bit Timer Register                                         | 249  |

| 11-12      | Timing After Compare Register Changes During Timer Counting                  | 250  |

# LIST OF FIGURES (4/8)

| Figure No. | Title                                                                            | Page |

|------------|----------------------------------------------------------------------------------|------|

| 12-1       | Block Diagram of Watch Timer                                                     | 252  |

| 12-2       | Format of Watch Timer Mode Control Register (WTM)                                |      |

| 12-3       | Operation Timing of Watch Timer/Interval Timer                                   |      |

| 13-1       | Watchdog Timer Block Diagram                                                     | 257  |

| 13-2       | Watchdog Timer Mode Register (WDM) Format                                        | 259  |

| 14-1       | A/D Converter Block Diagram                                                      | 264  |

| 14-2       | A/D Converter Mode Register (ADM) Format                                         | 267  |

| 14-3       | A/D Converter Input Selection Register (ADIS) Format                             | 268  |

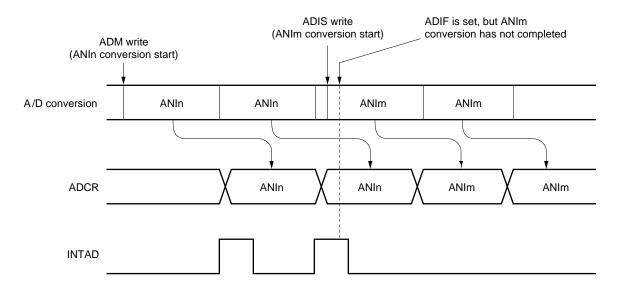

| 14-4       | Basic Operations of A/D Converter                                                | 270  |

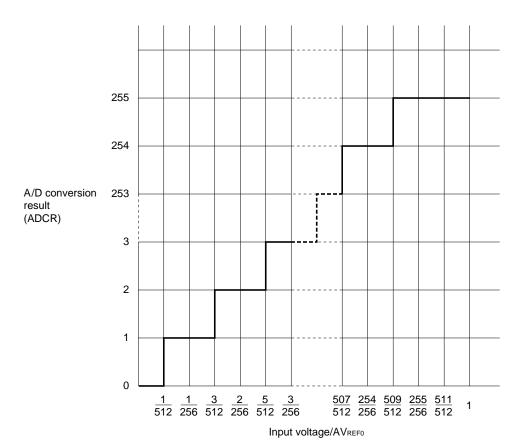

| 14-5       | Relationship between Analog Input Voltage and A/D Conversion Result              | 271  |

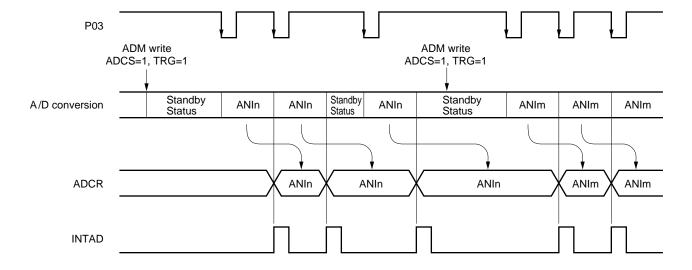

| 14-6       | A/D Conversion Operation by Hardware Start (with falling edge specified)         | 272  |

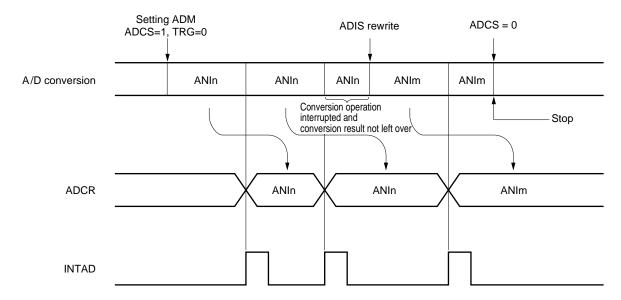

| 14-7       | A/D Conversion Operation by Software Start                                       | 273  |

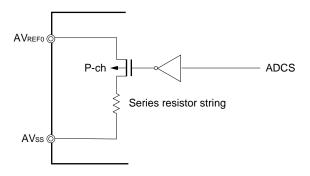

| 14-8       | Method to Reduce Current Dissipation in Standby Mode                             | 274  |

| 14-9       | Handling of Analog Input Pin                                                     | 275  |

| 14-10      | A/D Conversion End Interrupt Generation Timing                                   | 276  |

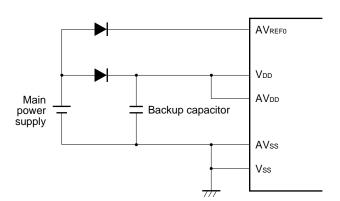

| 14-11      | Handling of AVDD Pin                                                             | 276  |

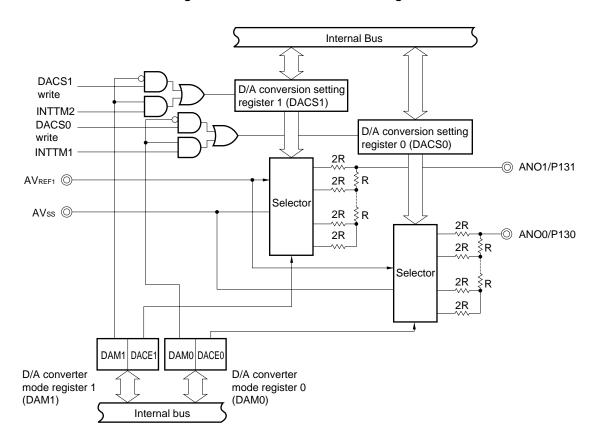

| 15-1       | D/A Converter Block Diagram                                                      | 280  |

| 15-2       | D/A Converter Mode Registers 0, 1 (DAM0, DAM1) Formats                           | 281  |

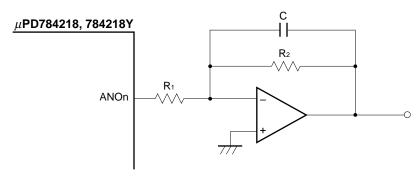

| 15-3       | Buffer Amp Insertion Example                                                     | 283  |

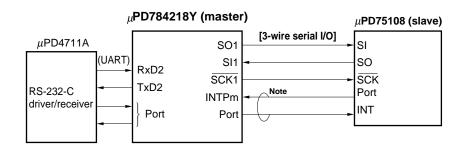

| 16-1       | Serial Interface Example                                                         | 286  |

| 17-1       | Switching Asynchronous Serial Interface Mode and 3-Wire Serial I/O Mode          | 288  |

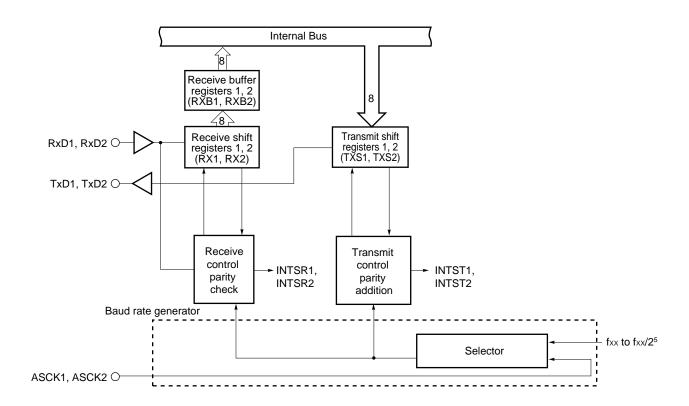

| 17-2       | Block Diagram in Asynchronous Serial Interface Mode                              | 290  |

| 17-3       | Asynchronous Serial Interface Mode Registers 1, 2 (ASIM1, ASIM2) Format          | 293  |

| 17-4       | Asynchronous Serial Interface Status Registers 1, 2 (ASIS1, ASIS2) Format        | 294  |

| 17-5       | Baud Rate Generator Control Registers 1, 2 (BRGC1, BRGC2) Format                 | 296  |

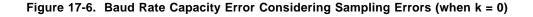

| 17-6       | Baud Rate Capacity Error Considering Sampling Errors (when k = 0)                | 303  |

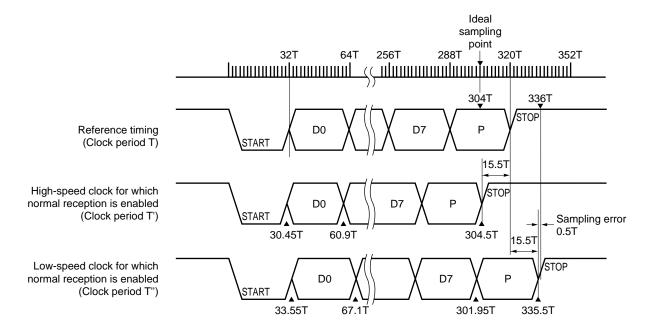

| 17-7       | Asynchronous Serial Interface Transmit/Receive Data Format                       | 304  |

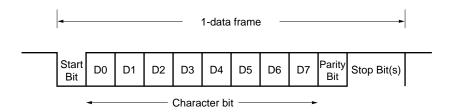

| 17-8       | Asynchronous Serial Interface Transmit Completion Interrupt Timing               | 306  |

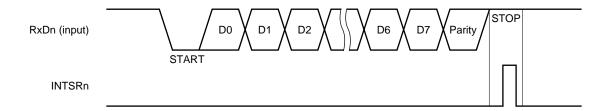

| 17-9       | Asynchronous Serial Interface Receive Completion Interrupt Timing                | 307  |

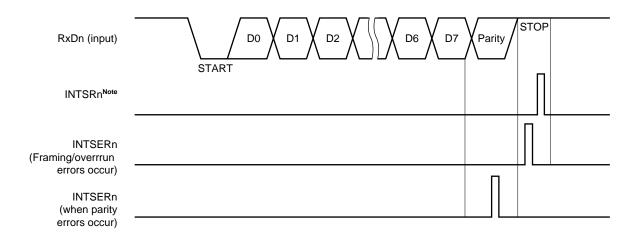

| 17-10      | Receive Error Timing                                                             | 308  |

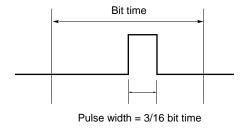

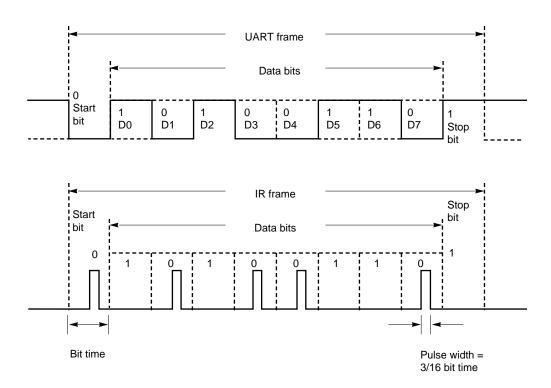

| 17-11      | Comparison of Infrared Data Transfer Mode and UART Mode Data Formats             | 309  |

| 17-12      | Block Diagram in 3-Wire Serial I/O Mode                                          | 314  |

| 17-13      | Serial Operation Mode Registers 1, 2 (CSIM1, CSIM2) Format                       | 315  |

| 17-14      | Serial Operation Mode Registers 1, 2 (CSIM1, CSIM2) Format                       | 316  |

| 17-15      | Serial Operation Mode Registers 1, 2 (CSIM1, CSIM2) Format                       | 317  |

| 17-16      | 3-Wire Serial I/O Mode Timing                                                    | 318  |

| 18-1       | Block Diagram of Clock-Synchronized Serial Interface (in 3-wire Serial I/O Mode) | 320  |

| 18-2       | Serial Operation Mode Register 0 (CSIM0) Format                                  | 321  |

# LIST OF FIGURES (5/8)

| Figure No.               | Title                                                                                         | Page |

|--------------------------|-----------------------------------------------------------------------------------------------|------|

| 18-3                     | Serial Operation Mode Register 0 (CSIM0) Format                                               | 222  |

| 18-4                     | Serial Operation Mode Register 0 (CSIMO) Format                                               |      |

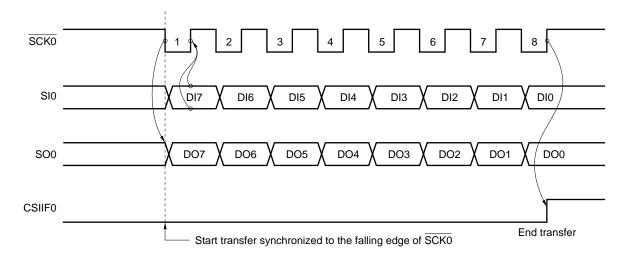

| 18- <del>4</del><br>18-5 | 3-Wire Serial I/O Mode Timing                                                                 |      |

| 10-3                     | 3-Wile Seliai I/O Mode Hilling                                                                | 324  |

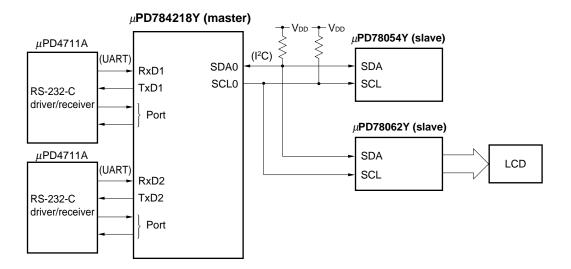

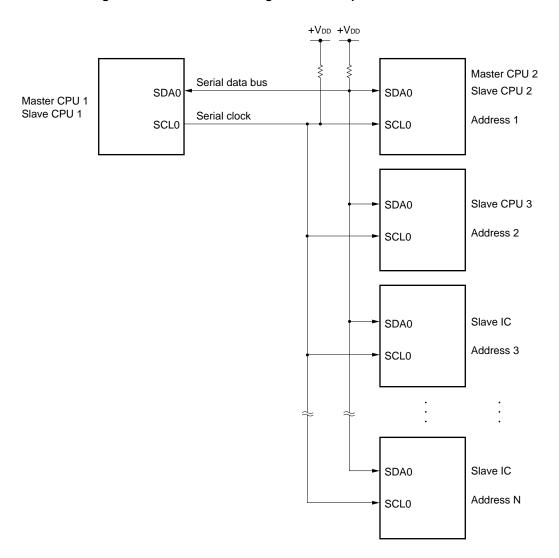

| 19-1                     | Serial Bus Configuration Example in I <sup>2</sup> C Bus Mode                                 | 326  |

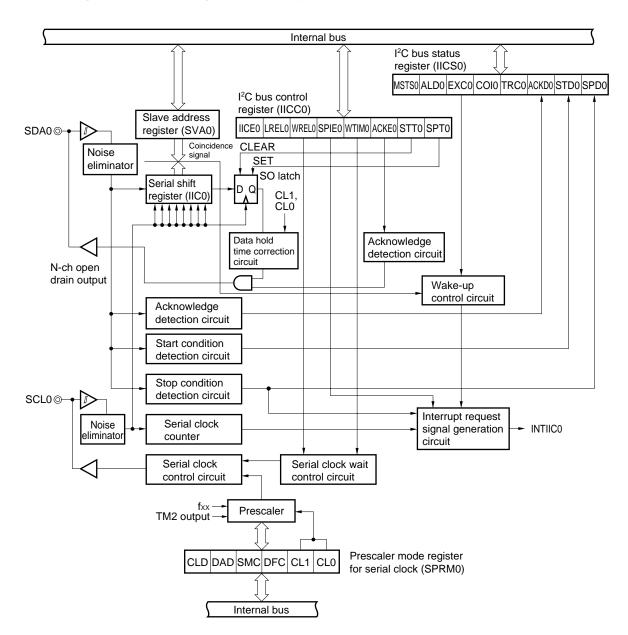

| 19-2                     | Block Diagram of Clock-synchronized Serial Interface (I <sup>2</sup> C Bus Mode)              | 327  |

| 19-3                     | I <sup>2</sup> C Bus Control Register (IICC0) Format                                          | 330  |

| 19-4                     | I <sup>2</sup> C Bus Status Register (IICS0) Format                                           | 335  |

| 19-5                     | Format of Prescaler Mode Register for Serial Clock (SPRM0)                                    | 339  |

| 19-6                     | Pin Configuration                                                                             | 341  |

| 19-7                     | Serial Data Transfer Timing of I <sup>2</sup> C Bus                                           | 342  |

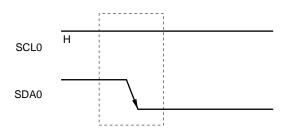

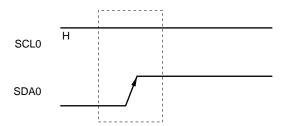

| 19-8                     | Start Condition                                                                               | 342  |

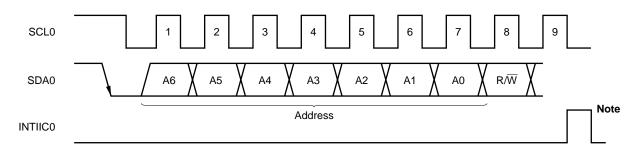

| 19-9                     | Address                                                                                       | 343  |

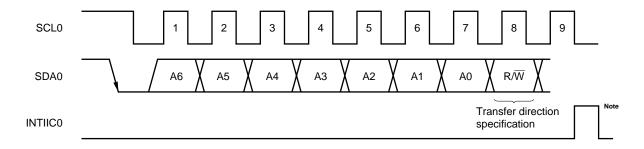

| 19-10                    | Transfer Direction Specification                                                              | 344  |

| 19-11                    | Acknowledge Signal                                                                            | 345  |

| 19-12                    | Stop Condition                                                                                | 346  |

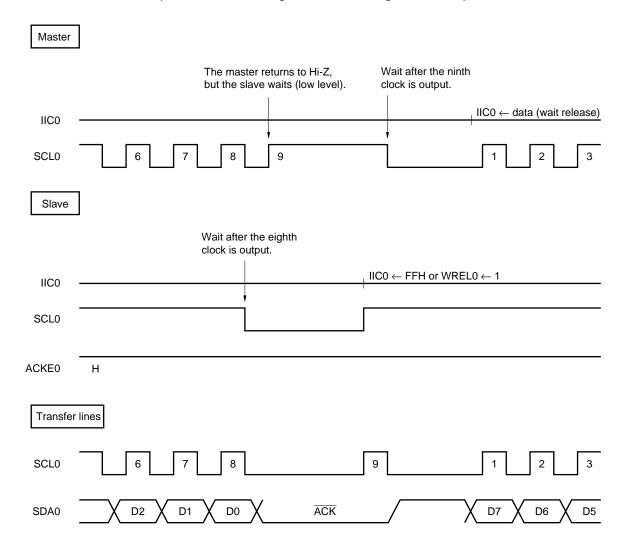

| 19-13                    | Wait Signal                                                                                   | 347  |

| 19-14                    | Example of Arbitration Timing                                                                 | 371  |

| 19-15                    | Timing of Communication Reservation                                                           | 374  |

| 19-16                    | Communication Reservation Acceptance Timing                                                   | 374  |

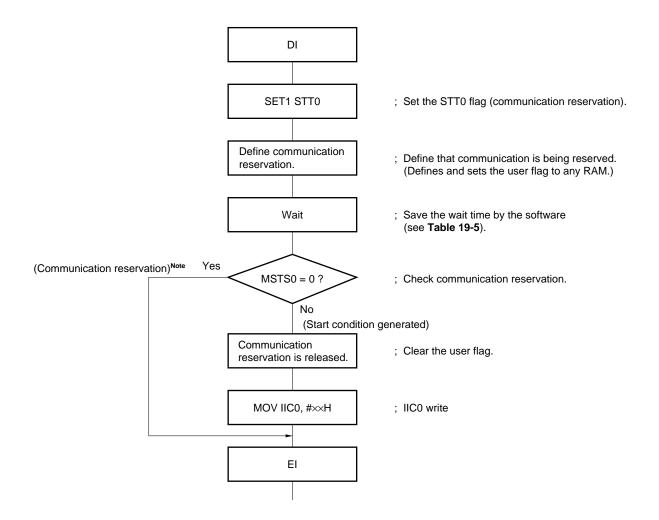

| 19-17                    | Communication Reservation Procedure                                                           | 375  |

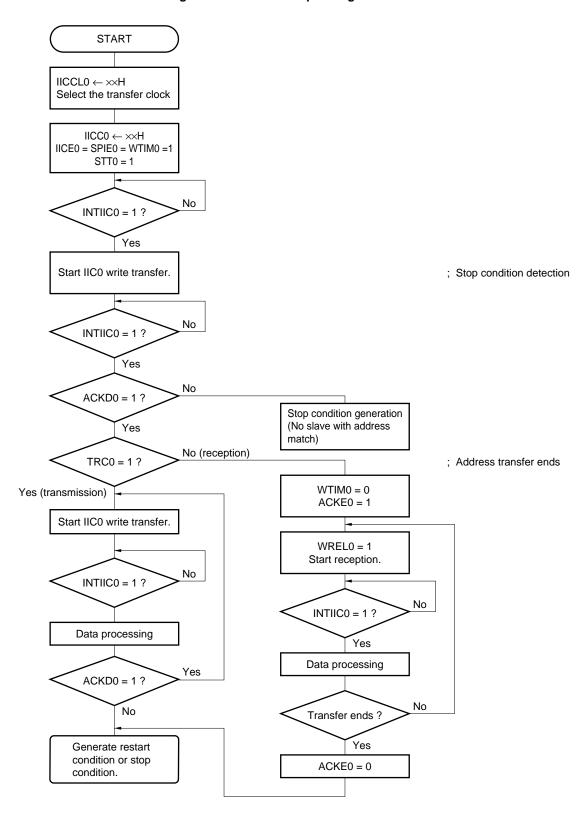

| 19-18                    | Master Operating Procedure                                                                    | 377  |

| 19-19                    | Slave Operating Procedure                                                                     | 378  |

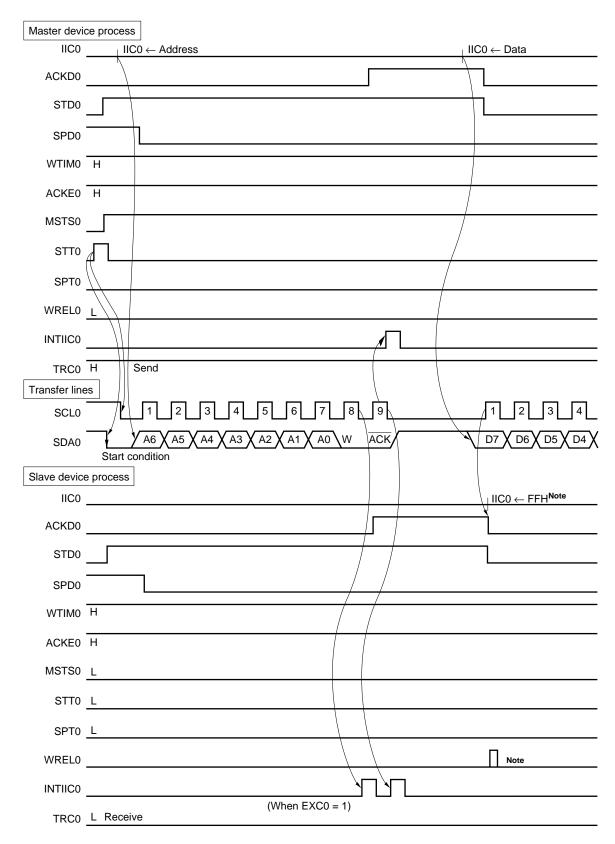

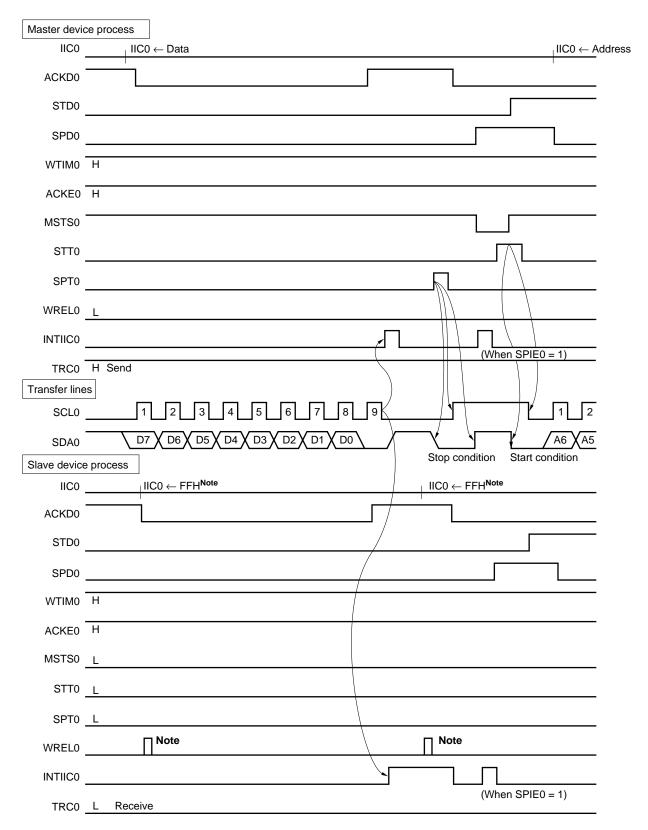

| 19-20                    | Master $\rightarrow$ Slave Communication Example (when master and slave select 9 clock waits) | 380  |

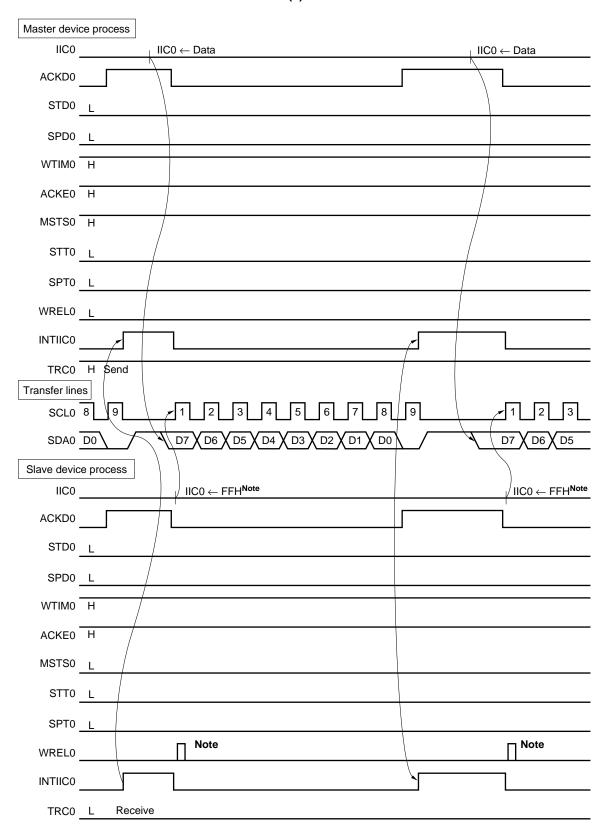

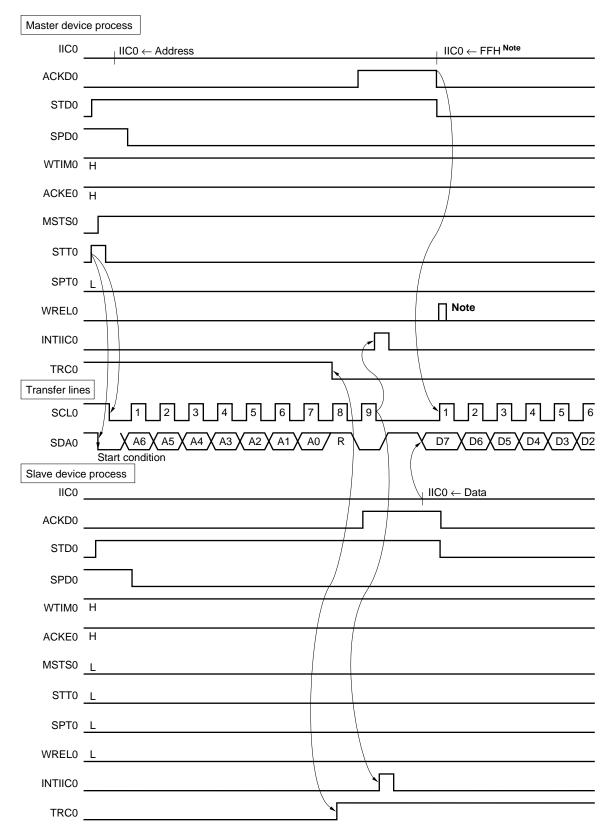

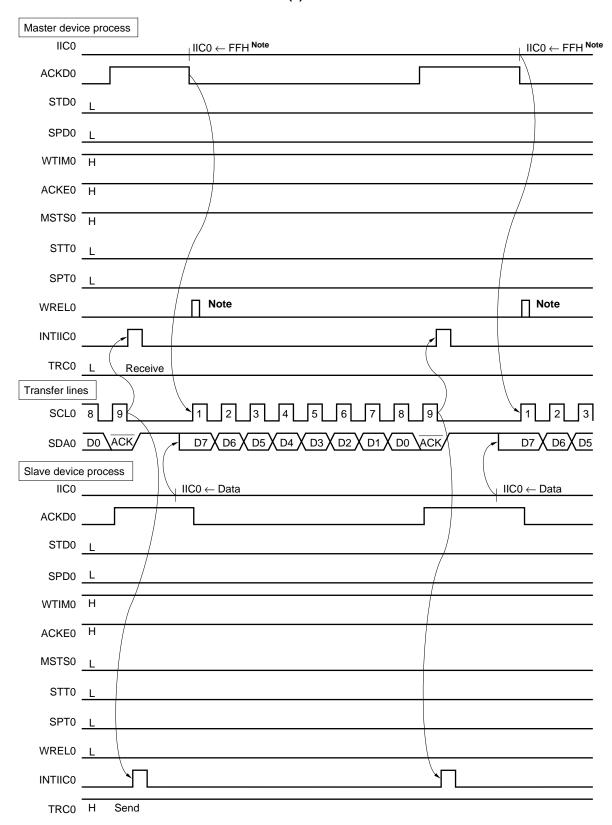

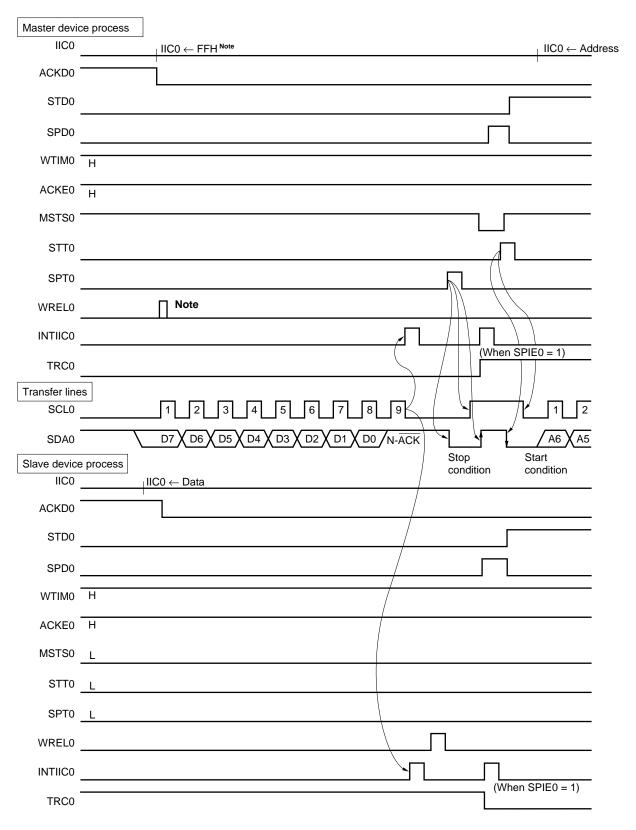

| 19-21                    | Slave $\rightarrow$ Master Communication Example (when master and slave select 9 clock waits) | 383  |

| 20-1                     | Remote Control Output Application Example                                                     | 387  |

| 20-2                     | Clock Output Function Block Diagram                                                           |      |

| 20-3                     | Clock Output Control Register (CKS) Format                                                    |      |

| 20-4                     | Port 2 Mode Register (PM2) Format                                                             |      |

|                          | · · · · · · · · · · · · · · · · · · ·                                                         |      |

| 21-1                     | Buzzer Output Function Block Diagram                                                          | 391  |

| 21-2                     | Clock Output Control Register (CKS) Format                                                    | 392  |

| 21-3                     | Port 2 Mode Register (PM2) Format                                                             | 393  |

| 22-1                     | Format of External Interrupt Rising Edge Enable Register (EGP0) and                           |      |

|                          | External Interrupt Falling Edge Enable Register (EGN0)                                        | 395  |

| 22-2                     | Edge Detection of P00 to P06 Pins                                                             | 396  |

| 23-1                     | Interrupt Control Register (xxICn)                                                            | 405  |

| 23-2                     | Format of Interrupt Mask Registers (MK0, MK1)                                                 |      |

| 23-3                     | Format of In-Service Priority Register (ISPR)                                                 |      |

| 23-4                     | Format of Interrupt Mode Control Register (IMC)                                               |      |

|                          | · · · · · · · · · · · · · · · · · · ·                                                         |      |

# LIST OF FIGURES (6/8)

| Figure No. | Title                                                                                      | Page |

|------------|--------------------------------------------------------------------------------------------|------|

| 23-5       | Format of Watchdog Timer Mode Register (WDM)                                               | 412  |

| 23-6       | Format of Interrupt Selection Control Register (SNMI)                                      |      |

| 23-7       | Format of Program Status Word (PSWL)                                                       |      |

| 23-8       | Context Switching Operation by Execution of BRKCS Instruction                              |      |

| 23-9       | Return from BRKCS Instruction Software Interrupt (RETCSB Instruction Operation)            |      |

| 23-10      | Non-Maskable Interrupt Request Acknowledgment Operations                                   | 418  |

| 23-11      | Interrupt Acknowledgment Processing Algorithm                                              | 422  |

| 23-12      | Context Switching Operation by Generation of Interrupt Request                             | 423  |

| 23-13      | Return from Interrupt that Uses Context Switching by Means of RETCS Instruction            | 424  |

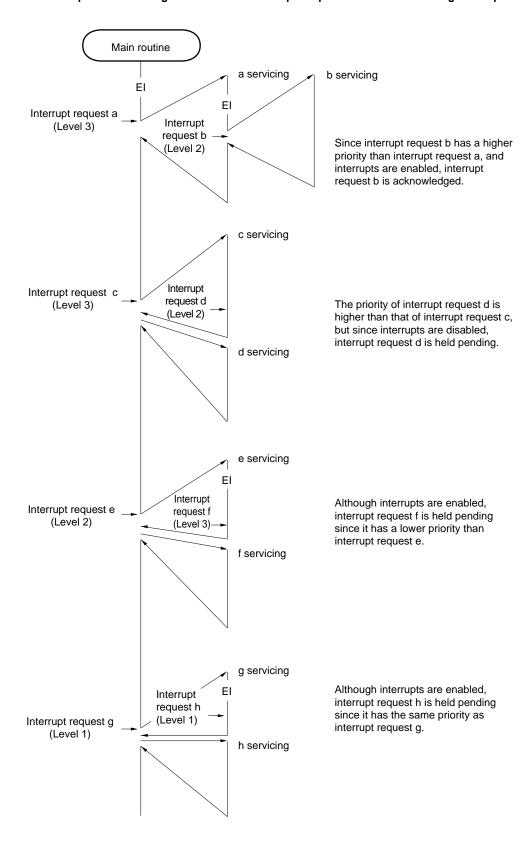

| 23-14      | Examples of Servicing When Another Interrupt Request is Generated During Interrupt Service | 426  |

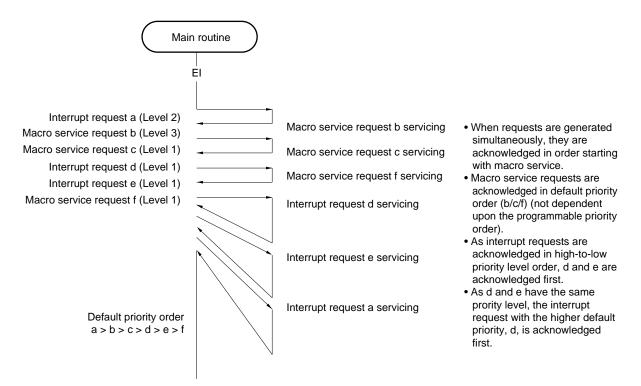

| 23-15      | Examples of Servicing of Simultaneously Generated Interrupts                               | 429  |

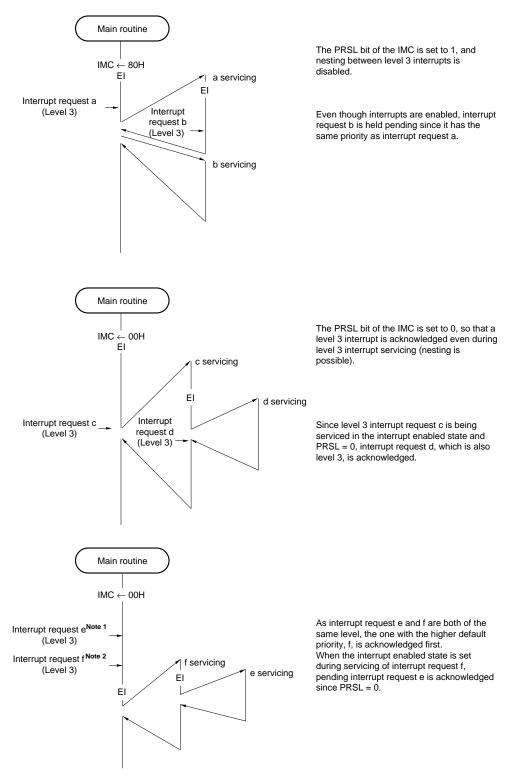

| 23-16      | Differences in Level 3 Interrupt Acknowledgment According to IMC Register Setting          | 430  |

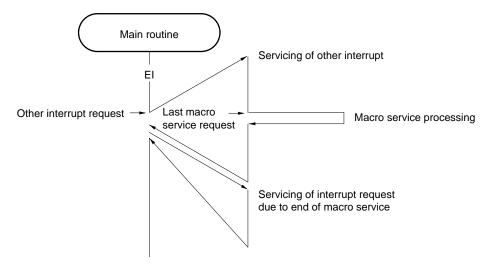

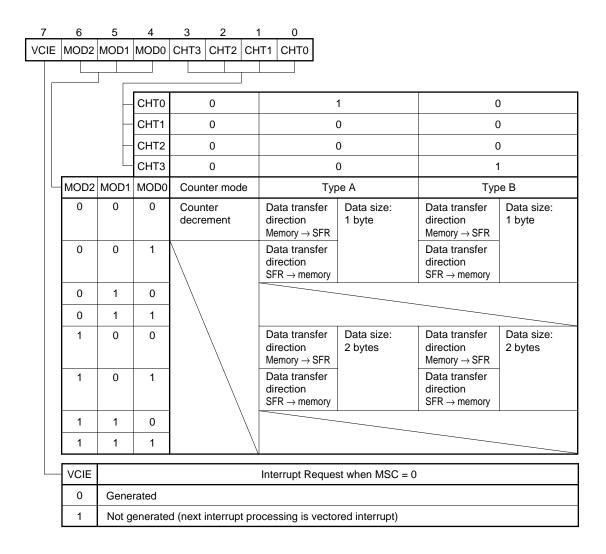

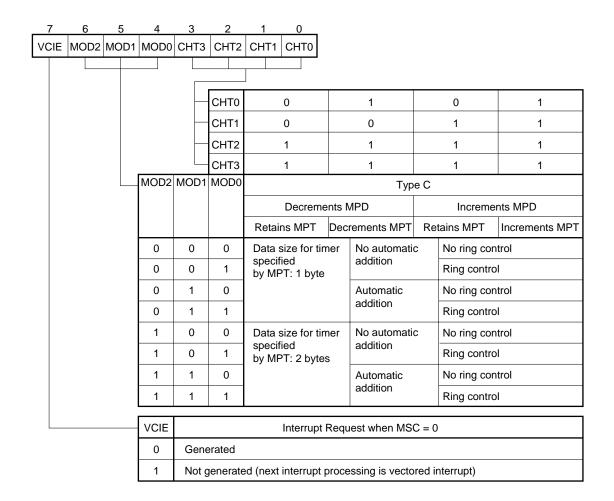

| 23-17      | Differences between Vectored Interrupt and Macro Service Processing                        | 431  |

| 23-18      | Macro Service Processing Sequence                                                          | 434  |

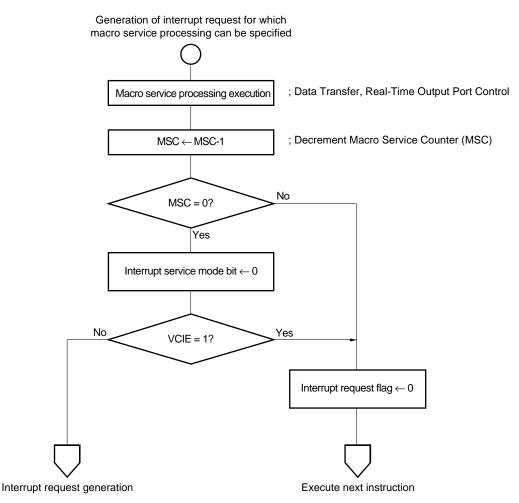

| 23-19      | Operation at End of Macro Service When VCIE = 0                                            | 436  |

| 23-20      | Operation at End of Macro Service When VCIE = 1                                            | 437  |

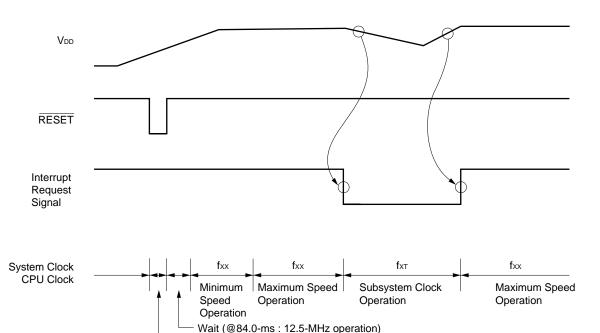

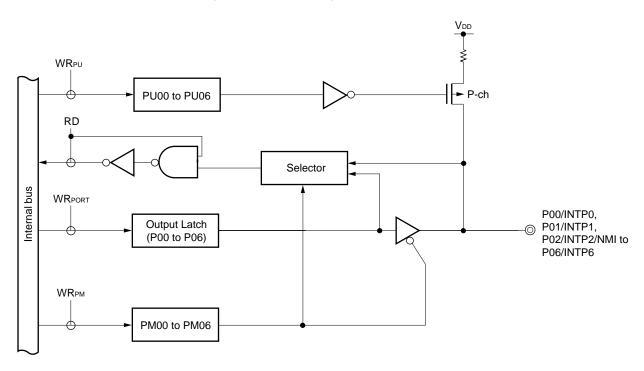

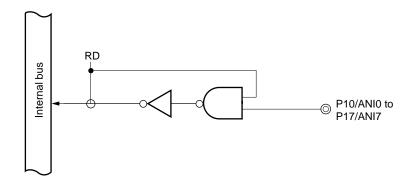

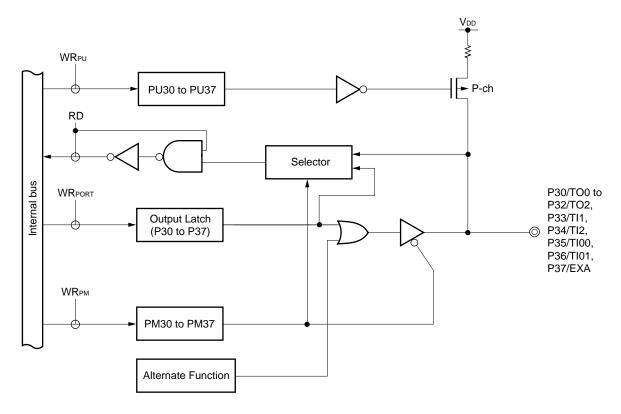

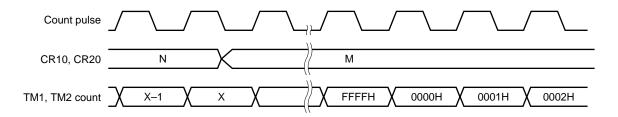

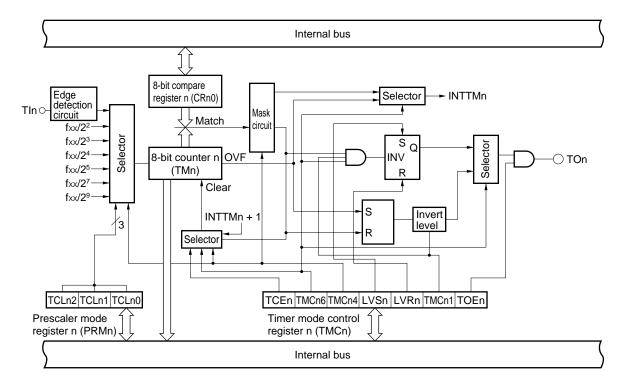

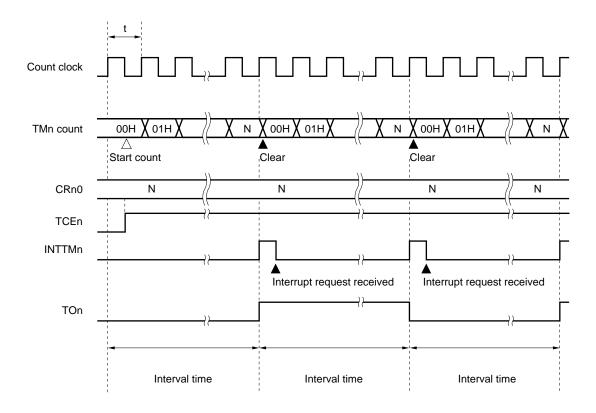

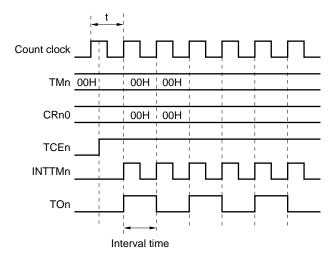

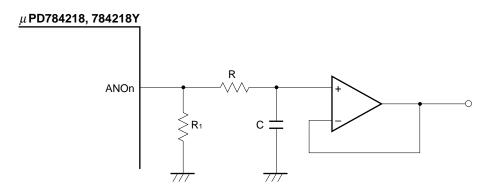

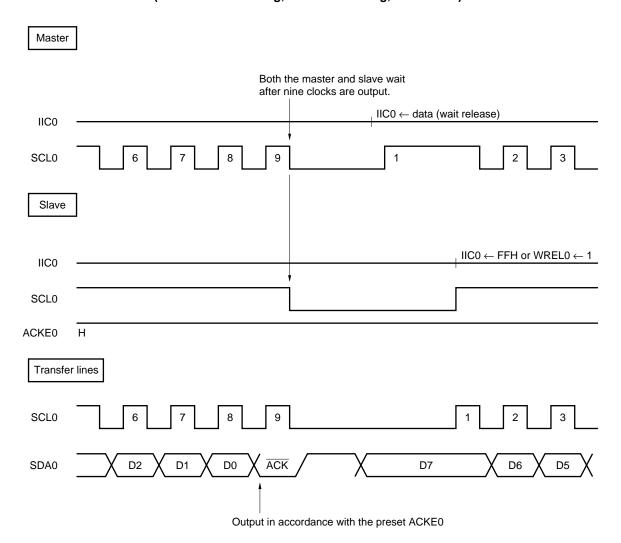

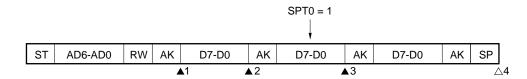

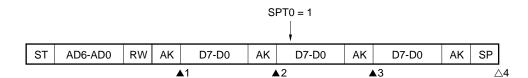

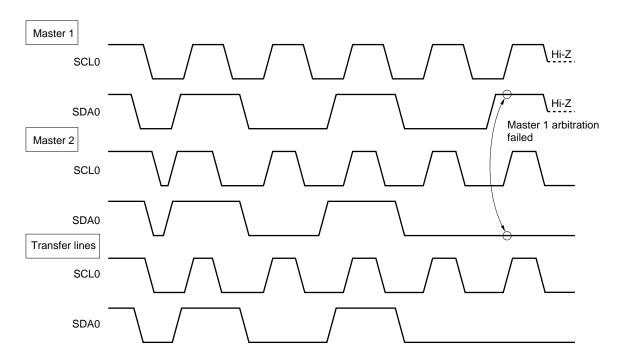

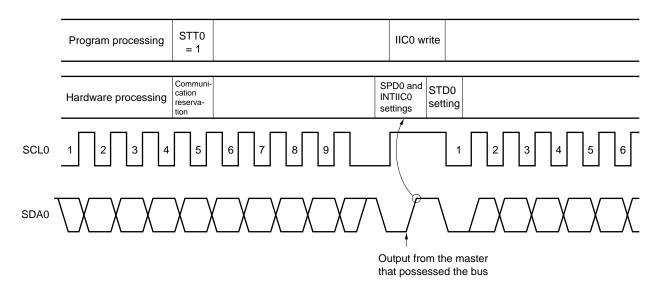

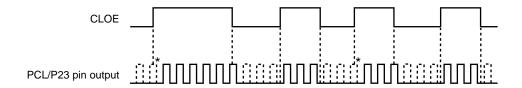

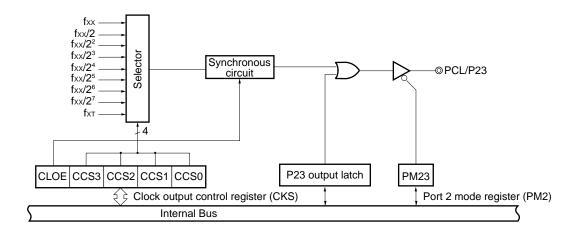

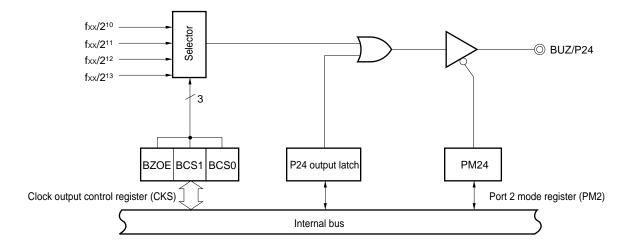

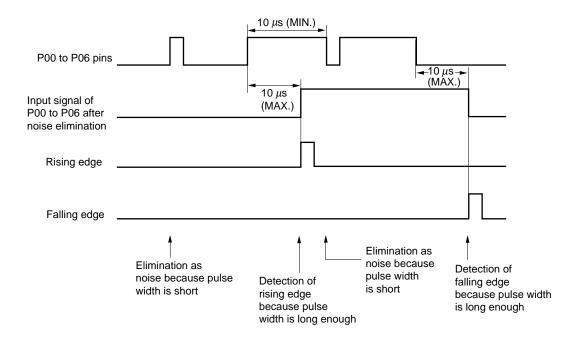

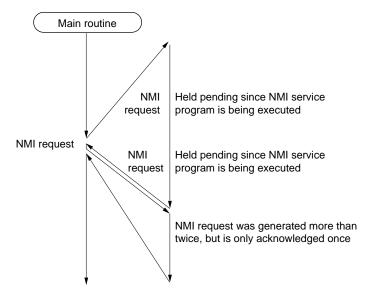

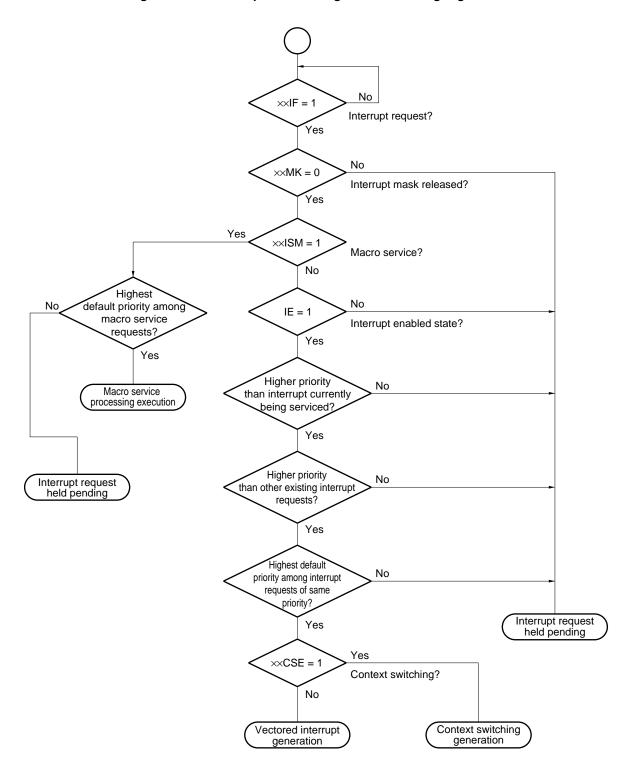

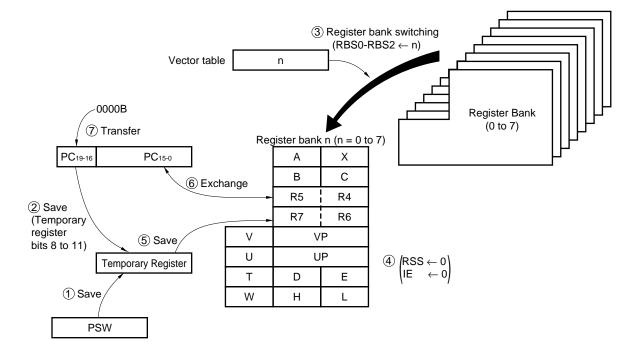

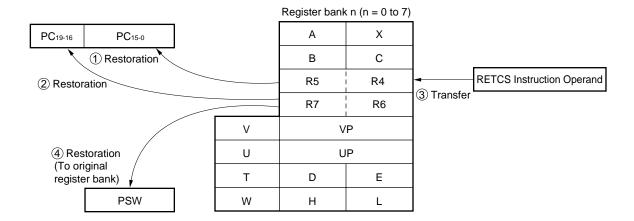

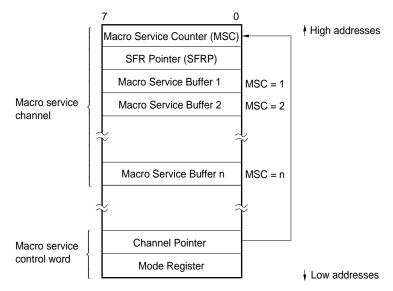

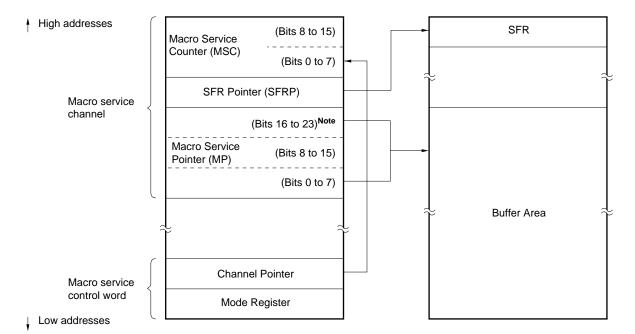

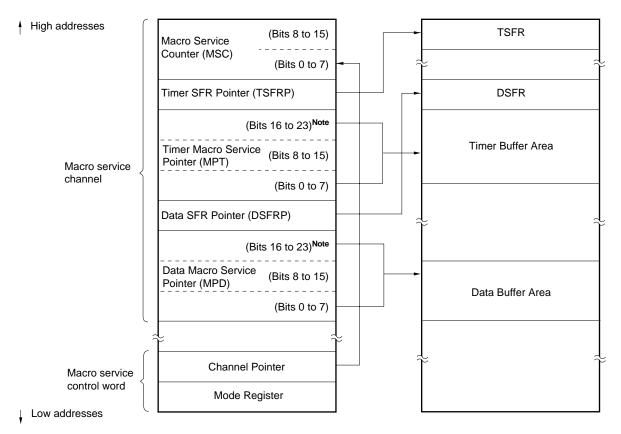

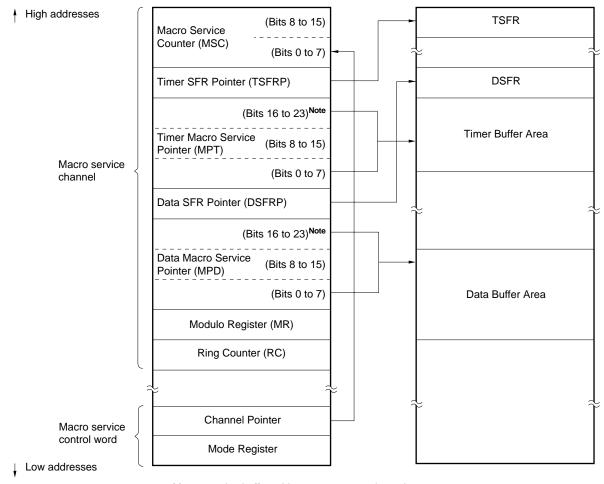

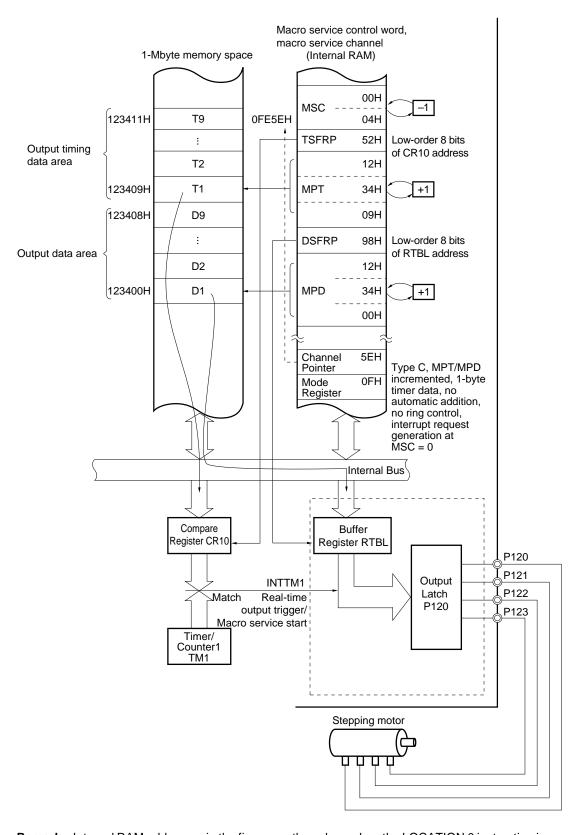

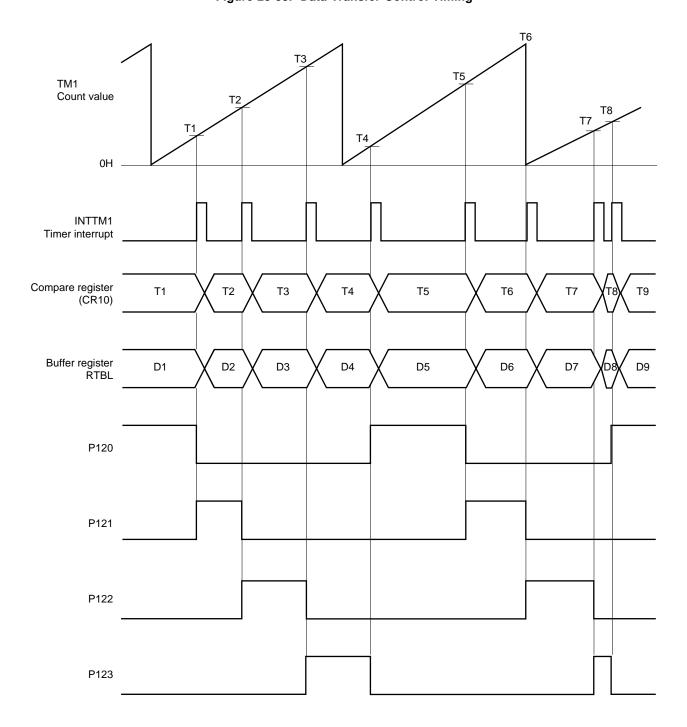

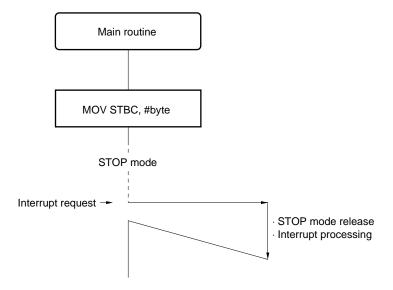

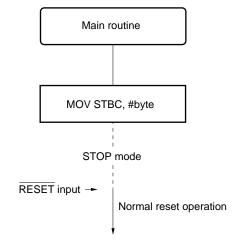

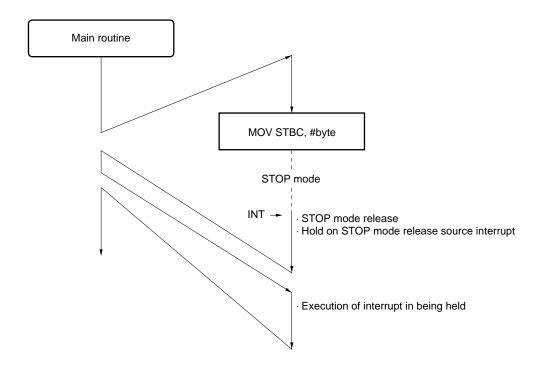

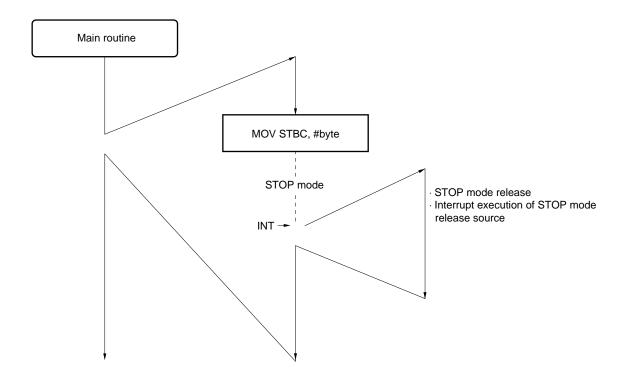

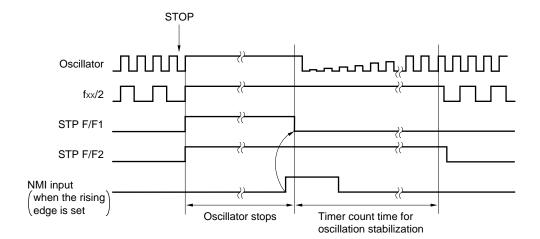

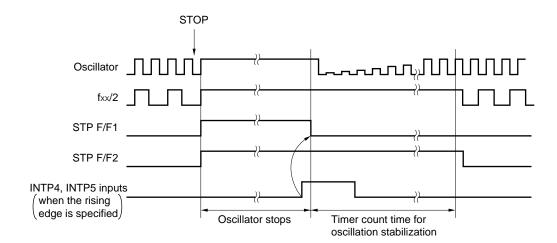

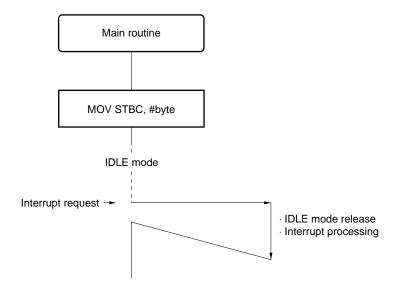

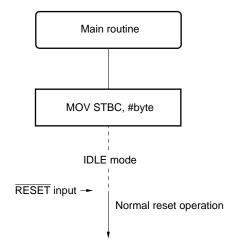

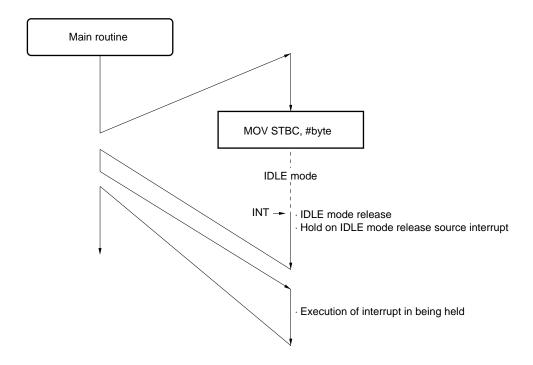

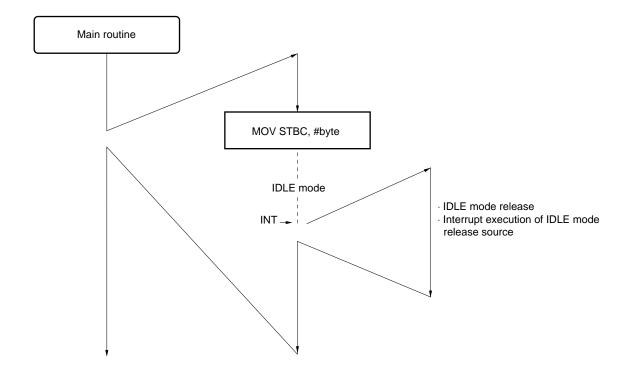

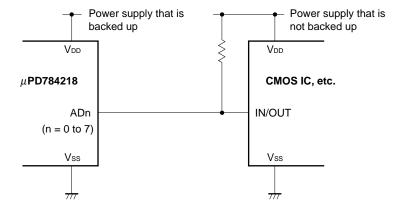

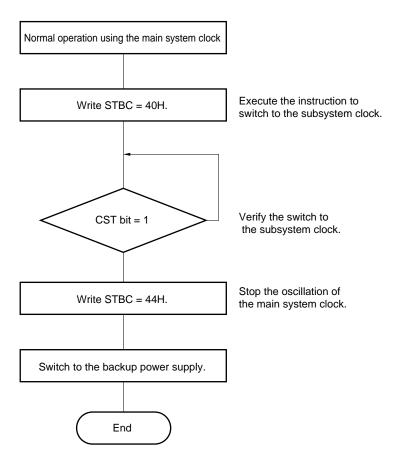

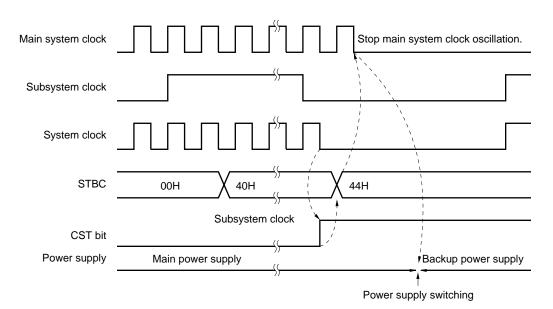

| 23-21      | Macro Service Control Word Format                                                          | 439  |